AP-578

2/21/97 12:57 PM 24329102.DOC

INTEL CONFIDENTIAL

(until publication date)

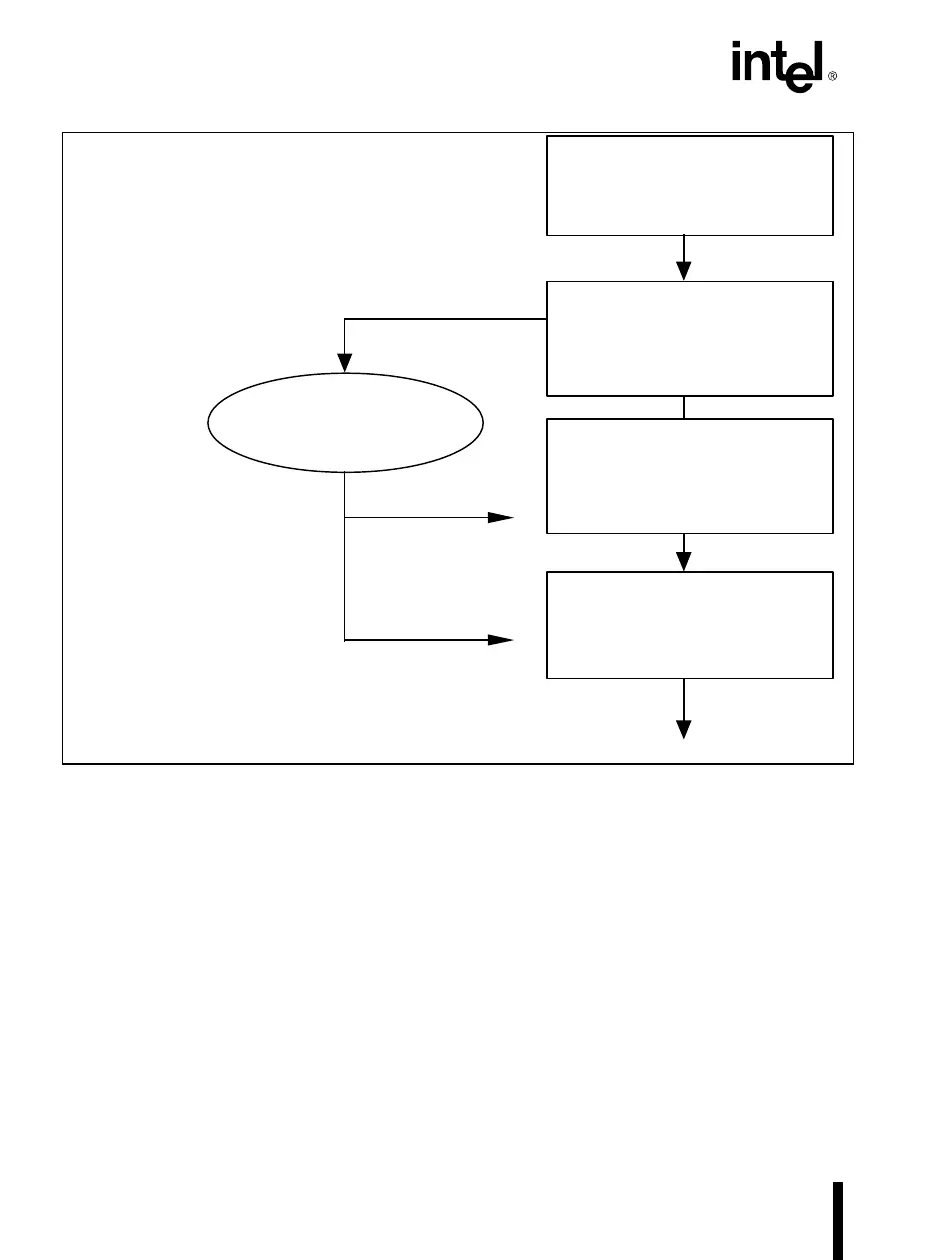

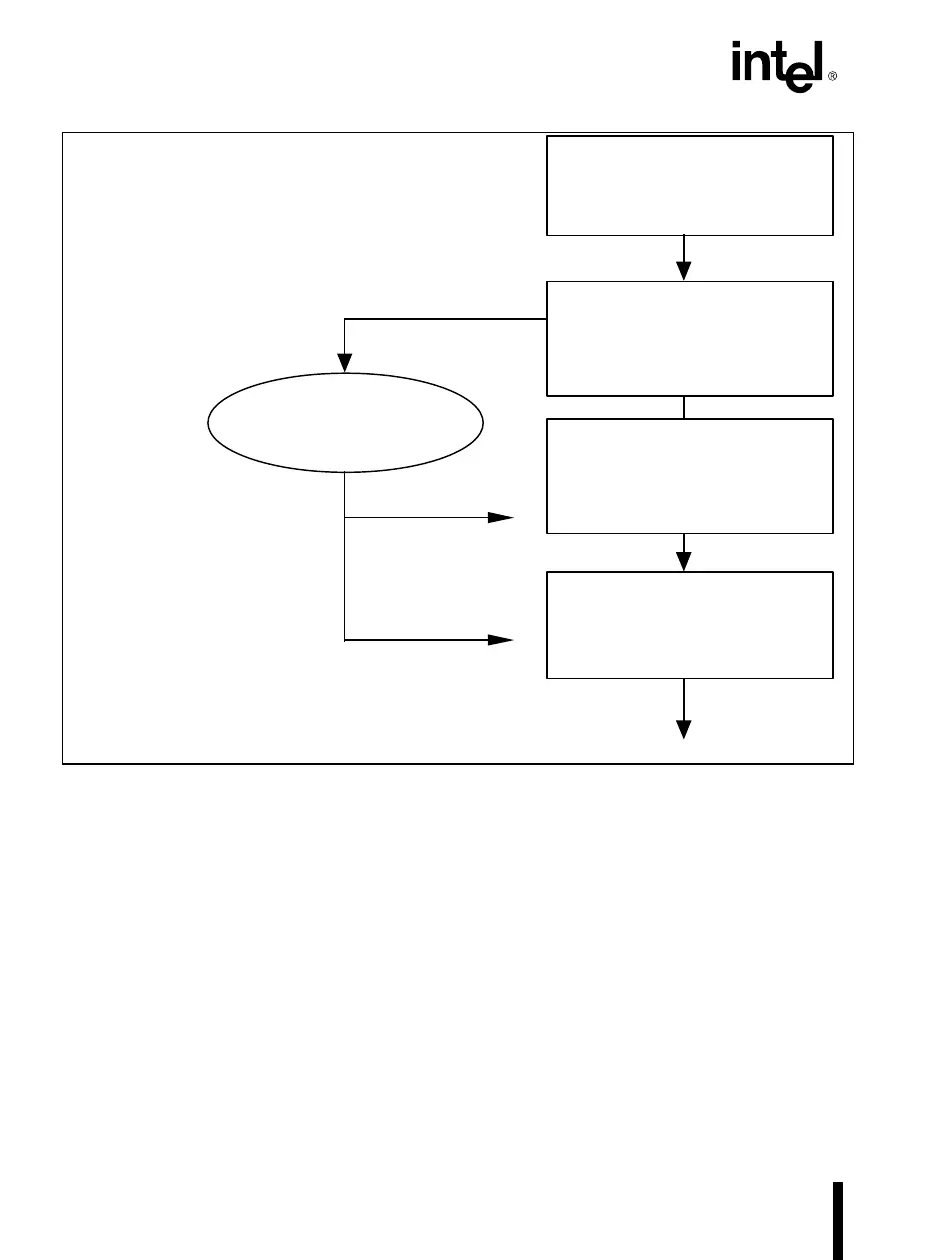

Exception generating

FP instruction

Start of the

“No-Wait” FP

instruction

Assertion Of FERR#

by the processor

System Dependent

Delay

External Interrupt

Sampling Window

Window CLOSED

Case I

Case II

Assertion Of INTR

pin by the system

Figure 3: Timing of Receipt of External Interrupt

Figure 3 assumes that a floating-point instruction

which generates a “deferred” error (as defined

above in the Section 2.3.1), which asserts the

FERR# pin only on encountering the next floating-

point instruction, causes an unmasked numeric

exception. Assume that the next floating-point

instruction following this instruction is one of the

“No-Wait” floating-point instructions. The FERR#

pin is asserted by the processor to indicate the

pending exception on encountering the “No-Wait”

floating-point instruction. After the assertion of the

FERR# pin the “No-Wait” floating-point instruction

opens a window where the pending external

interrupts are sampled.

Then there are two cases possible depending on

the timing of the receipt of the interrupt via the INTR

pin (asserted by the system in response to the

FERR# pin) by the processor.

Case 1

If the system responds to the assertion of FERR#

pin by the “No-Wait” floating-point instruction via the

INTR pin during this window then the interrupt is

serviced first, before resuming the execution of the

“No-Wait” floating-point instruction.

Case 2

If the system responds via the INTR pin after the

window has closed then the interrupt is recognized

only at the next instruction boundary.

There are two other ways, in addition to Case I

above, in which a “No-Wait” floating-point

instruction can service a numeric exception inside

its interrupt window. First, the first floating-point

error condition could be of the “immediate” category

(as defined in Section 2.3.1) that assert FERR#

Loading...

Loading...