3/24/97 3-10 XA Memory Organization

3.5 Code Memory

Code memory starts at address 0 and extends to the highest valid address in the implementation,

at maximum, FFFFFFh. External Code Memory (off-chip) starts at the first address following the

highest Internal Code Memory (on-chip) location, if any. If code memory is present on-chip, it

always starts at location 0.

The upper sixteen 64K byte code pages (addresses F00000 through FFFFFF hexadecimal) are

reserved for special functions in XA derivatives. The same address range is reserved in the data

memory space, see section 3.4.

3.5.1 Alignment in Code Memory

As instructions are variable in length, from 1 to 6 bytes (see Chapter 6), instructions in code

memory can be located at odd addresses. As described in Chapter 6, instruction branch targets,

i.e., targets of jumps, calls, branches, traps, and interrupts must be aligned on an even address.

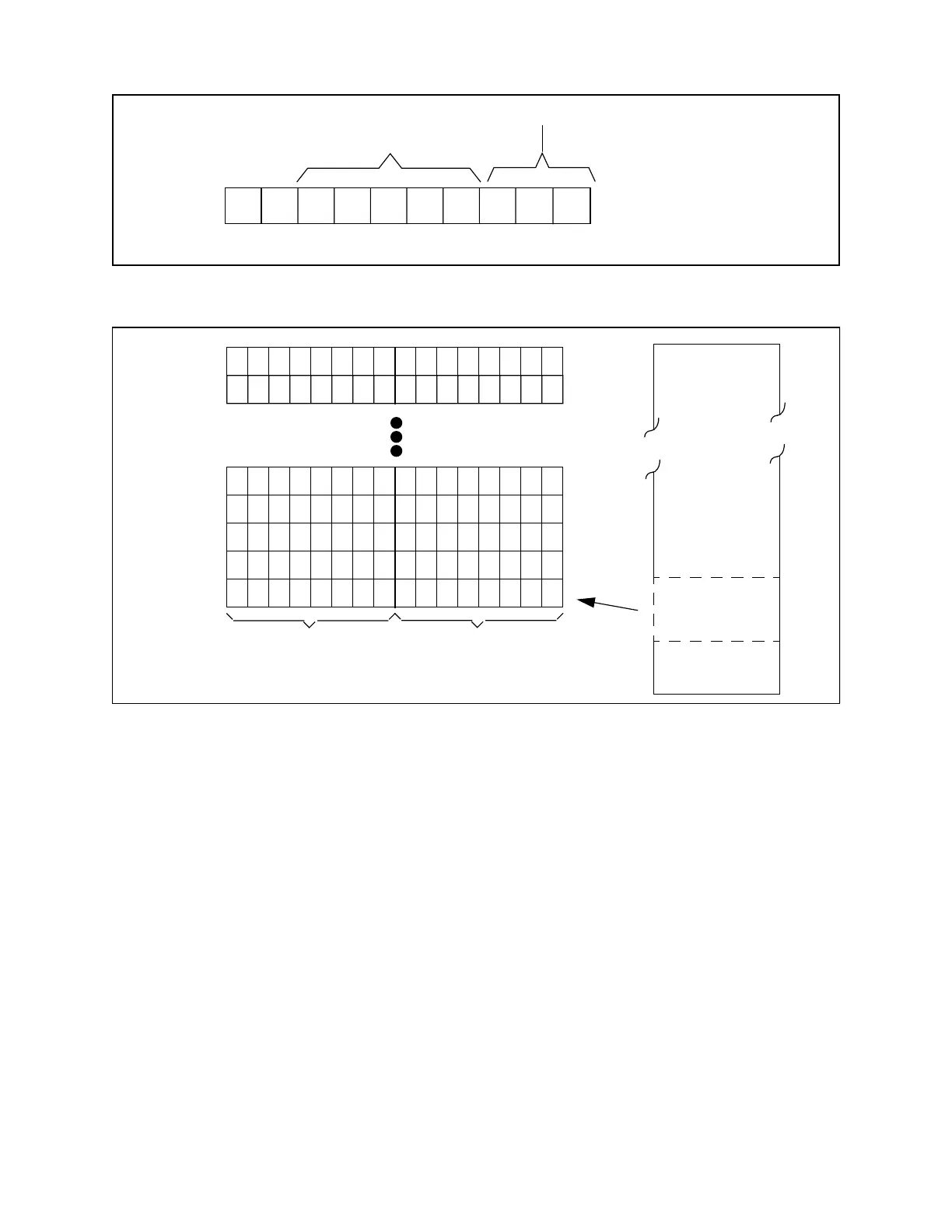

Figure 3.10 Bit address generation in direct memory space

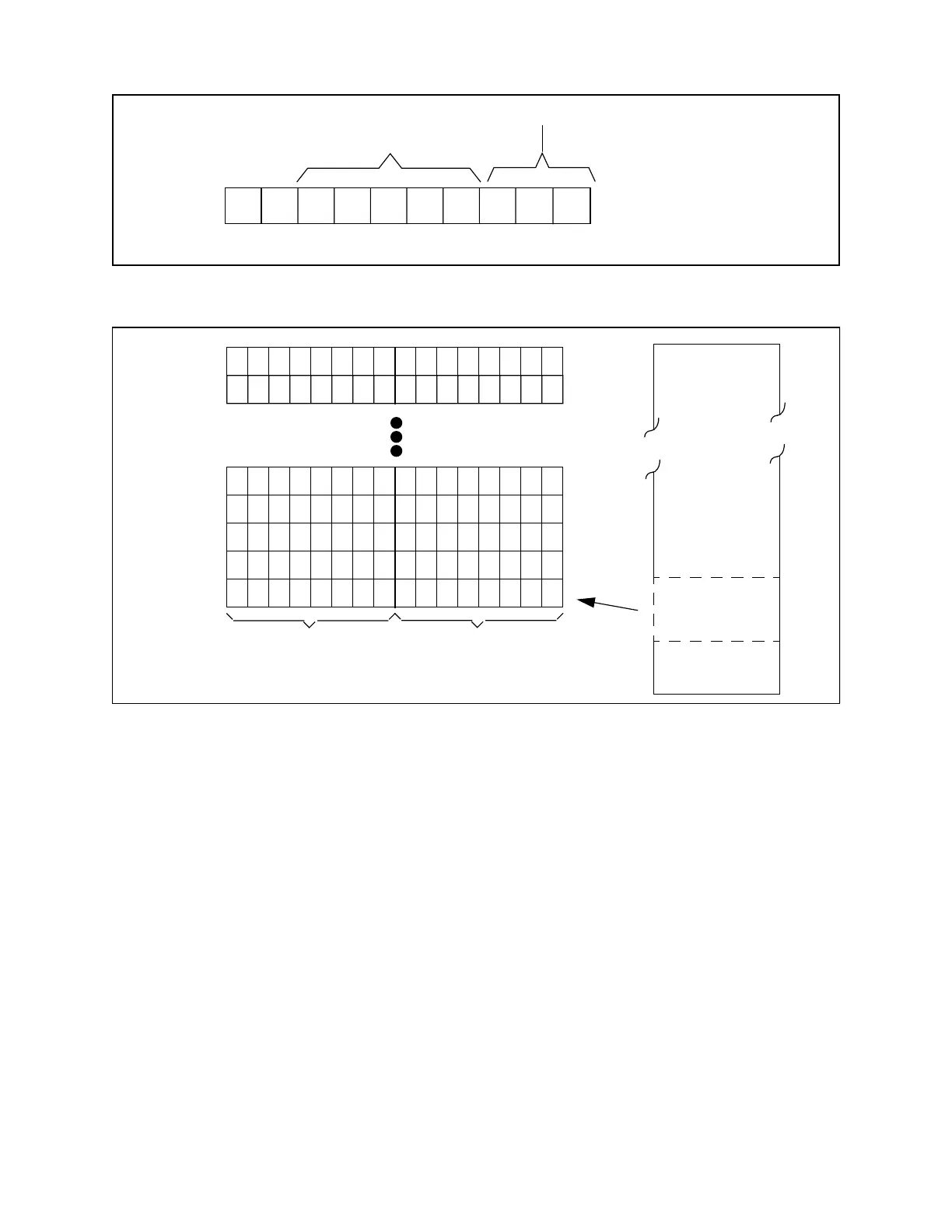

Figure 3.11 Direct memory bit addressing

9 8 7 6 5 4 3 2 1 0

byte offset from 20h

identifies 1 of 8 bits in a byte.

01

Segment n

20h

3Fh

3Eh

1EF 1EE 1ED 1EC 1EB 1EA 1E9 1E8 1E7 1E6 1E5 1E4 1E3 1E2 1E1 1E0

byte at odd address

byte even address

28h

14F 14E 14D 14C 14B 14A 149 148 147 146 145 144 143 142 141 140

26h

13F 13E 13D 13C 13B 13A 139 138 137 136 135 134 133 132 131 130

24h

12F 12E 12D 12C 12B 12A 129 128 127 126 125 124 123 122 121 120

22h

11F 11E 11D 11C 11B 11A 119 118 117 116 115 114 113 112 111 110

20h

10F 10E 10D 10C 10B 10A 109 108 107 106 105 104 103 102 101 100

3Fh

1FF 1FE 1FD 1FC 1FB 1FA 1F9 1F8 1F7 1F6 1F5 1F4 1F3 1F2 1F1 1F0

Loading...

Loading...