Philips Semiconductors Product specification

80C31/80C32

80C51 8-bit microcontroller family

128/256 byte RAM ROMless low voltage (2.7V–5.5V),

low power, high speed (33 MHz)

2000 Aug 07

30

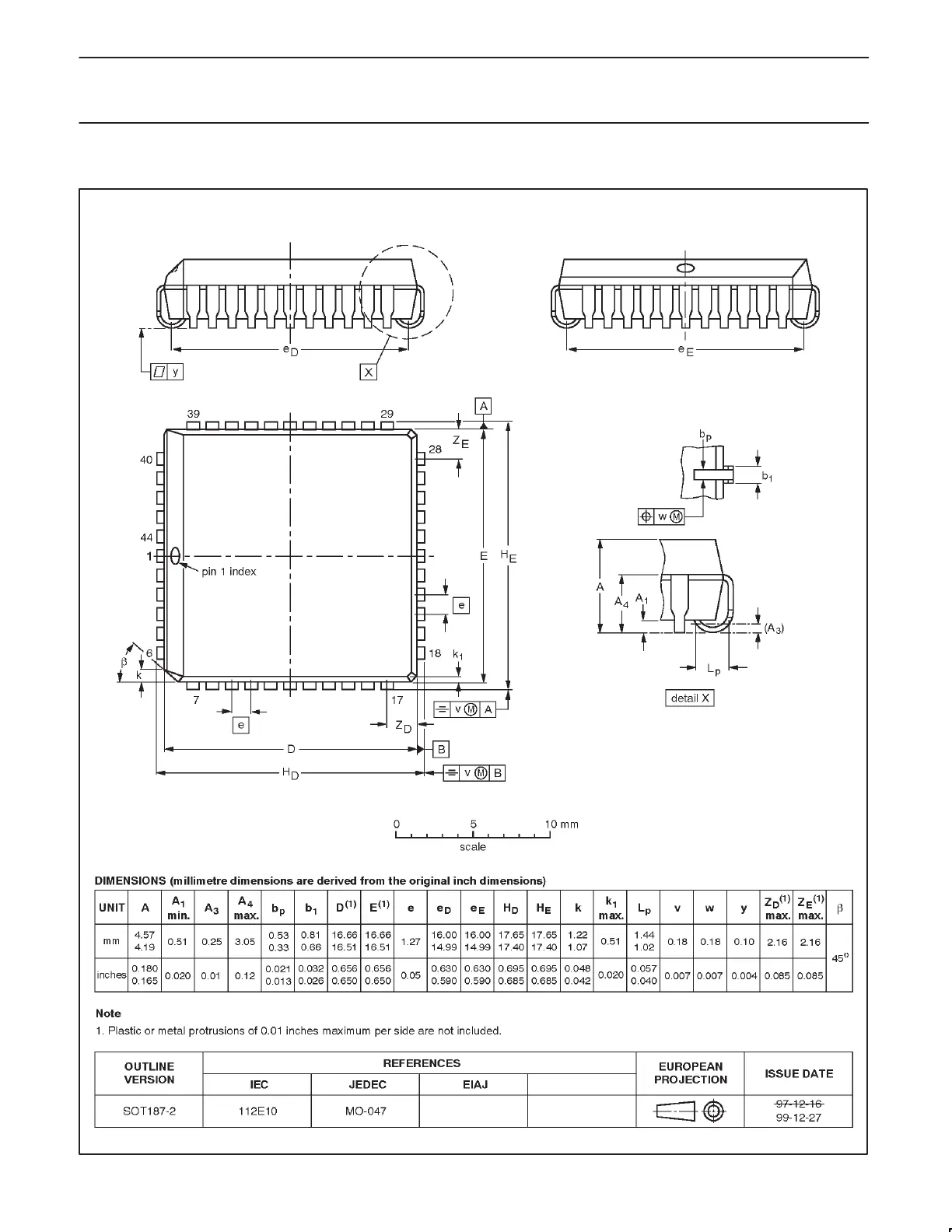

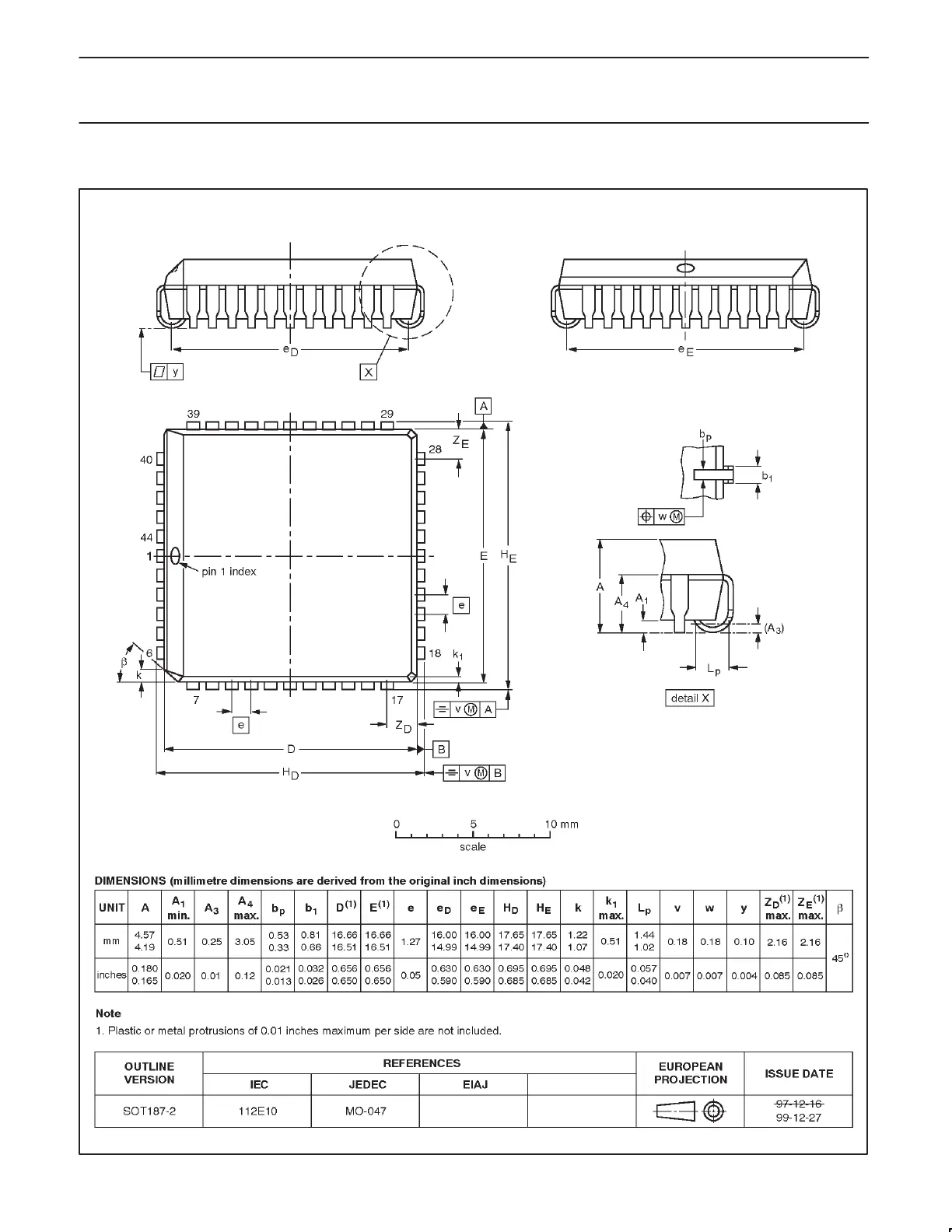

PLCC44: plastic leaded chip carrier; 44 leads SOT187-2

Loading...

Loading...