82C54

A.C. CHARACTERISTICS (Continued)

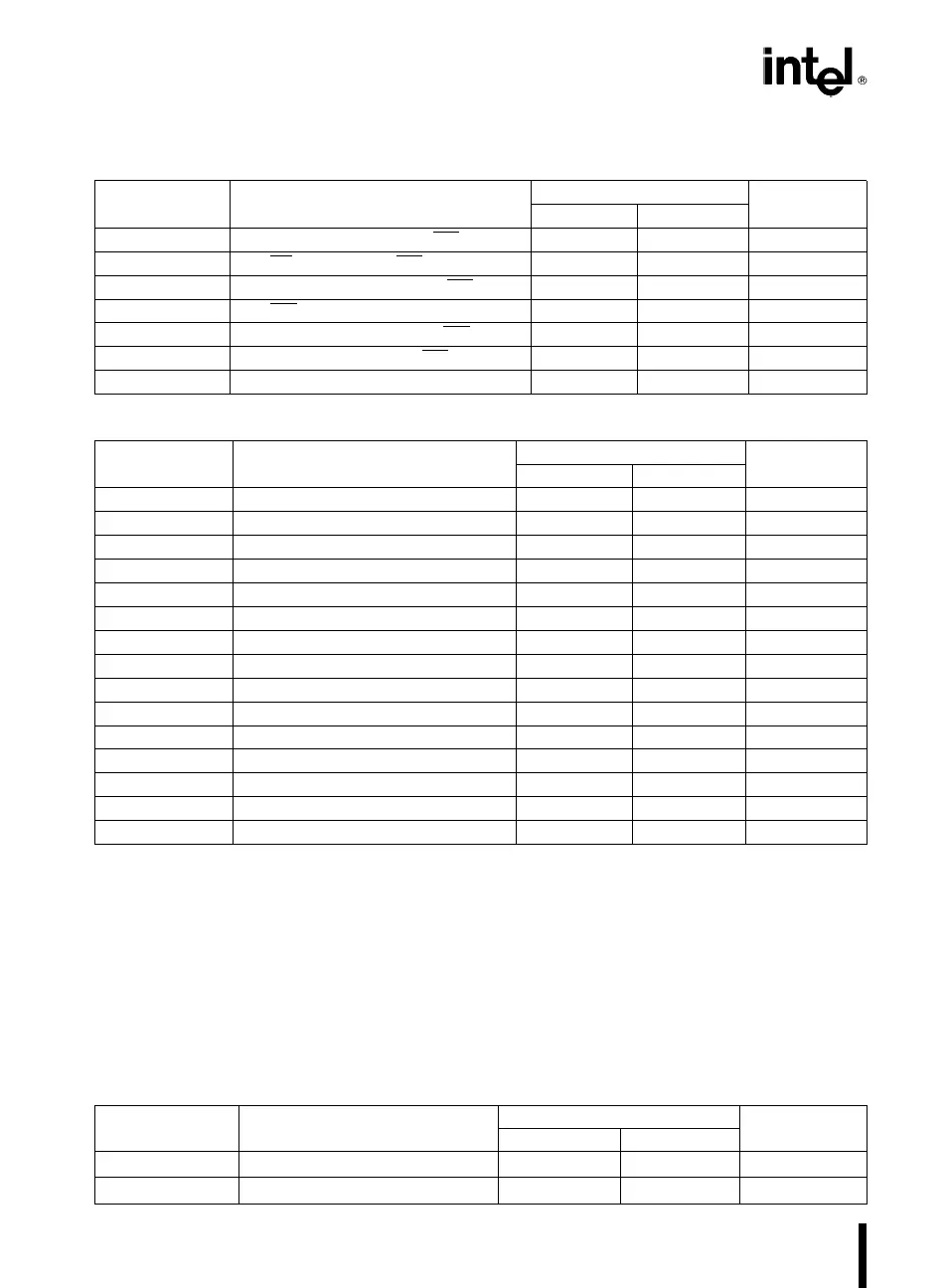

WRITE CYCLE

Symbol Parameter

82C54-2

Units

Min Max

t

AW

Address Stable Before WR

v

0ns

t

SW

CS Stable Before WR

v

0ns

t

WA

Address Hold Time After WR

u

0ns

t

WW

WR Pulse Width 95 ns

t

DW

Data Setup Time Before WR

u

95 ns

t

WD

Data Hold Time After WR

u

0ns

t

RV

Command Recovery Time 165 ns

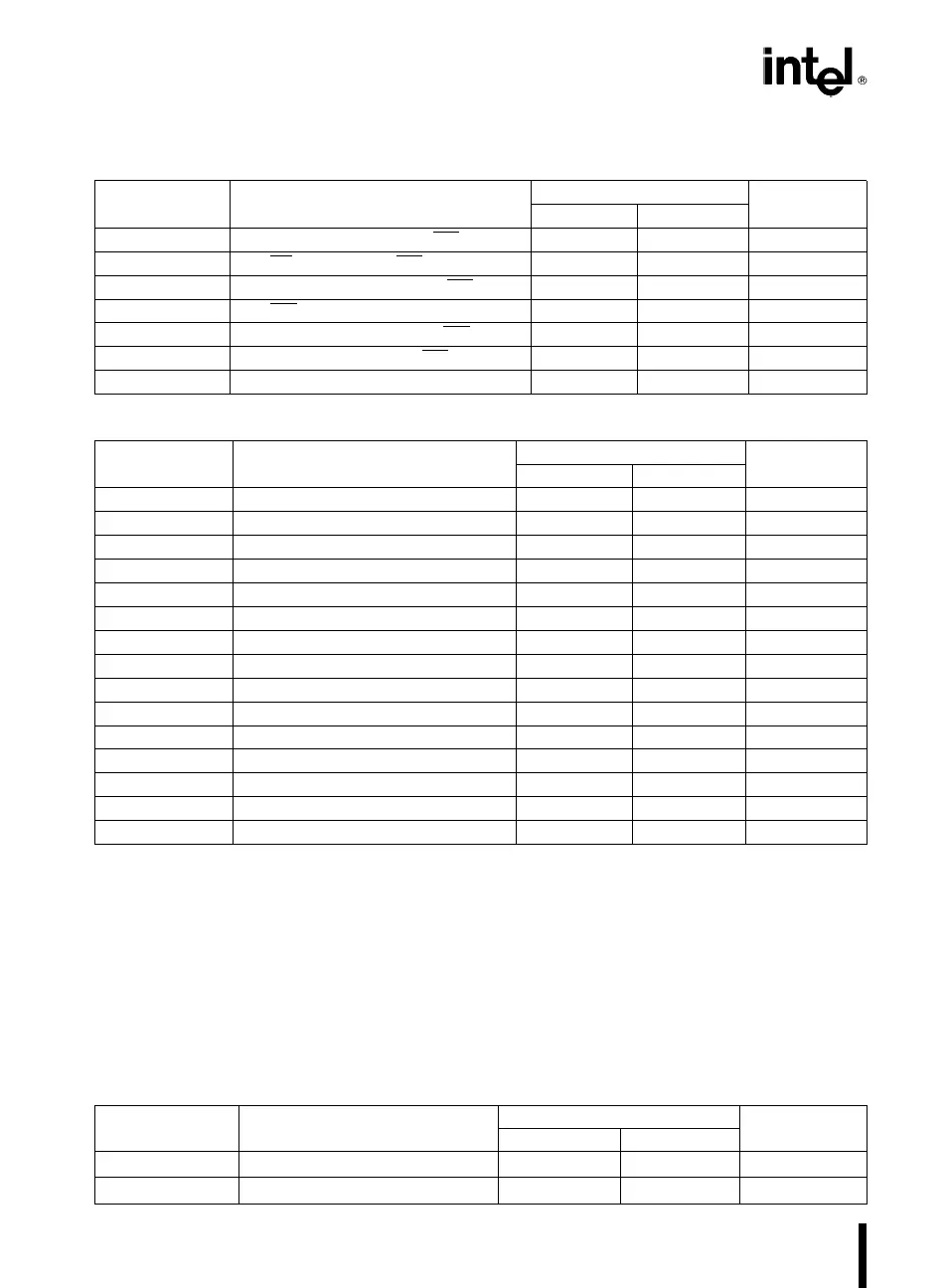

CLOCK AND GATE

Symbol Parameter

82C54-2

Units

Min Max

t

CLK

Clock Period 100 DC ns

t

PWH

High Pulse Width 30

(3)

ns

t

PWL

Low Pulse Width 50

(3)

ns

T

R

Clock Rise Time 25 ns

t

F

Clock Fall Time 25 ns

t

GW

Gate Width High 50 ns

t

GL

Gate Width Low 50 ns

t

GS

Gate Setup Time to CLK

u

40 ns

t

GH

Gate Hold Time After CLK

u

50

(2)

ns

T

OD

Output Delay from CLK

v

100 ns

t

ODG

Output Delay from Gate

v

100 ns

t

WC

CLK Delay for Loading

(4)

055ns

t

WG

Gate Delay for Sampling

(4)

b

540 ns

t

WO

OUT Delay from Mode Write 240 ns

t

CL

CLK Set Up for Count Latch

b

40 40 ns

NOTES:

2. In Modes 1 and 5 triggers are sampled on each rising clock edge. A second trigger within 70 ns for the 82C54-2 of the

rising clock edge may not be detected.

3. Low-going glitches that violate t

PWH

,t

PWL

may cause errors requiring counter reprogramming.

4. Except for Extended Temp., See Extended Temp. A.C. Characteristics below.

5. Sampled not 100% tested. T

A

e

25

§

C.

6. If CLK present at T

WC

min then Count equals N

a

2 CLK pulses, T

WC

max equals Count N

a

1 CLK pulse. T

WC

min to

T

WC

max, count will be either N

a

1orN

a

2 CLK pulses.

7. In Modes 1 and 5, if GATE is present when writing a new Count value, at T

WG

min Counter will not be triggered, at T

WG

max Counter will be triggered.

8. If CLK present when writing a Counter Latch or ReadBack Command, at T

CL

min CLK will be reflected in count value

latched, at T

CL

max CLK will not be reflected in the count value latched. Writing a Counter Latch or ReadBack Command

between T

CL

min and T

WL

max will result in a latched count vallue which is

g

one least significant bit.

EXTENDED TEMPERATURE (T

A

eb

40

§

Cto

a

85

§

C for Extended Temperature)

Symbol Parameter

82C54-2

Units

Min Max

t

WC

CLK Delay for Loading

b

25 25 ns

t

WG

Gate Delay for Sampling

b

25 25 ns

16

Loading...

Loading...