130 b EDN S

EPTEMBER 24, 1998

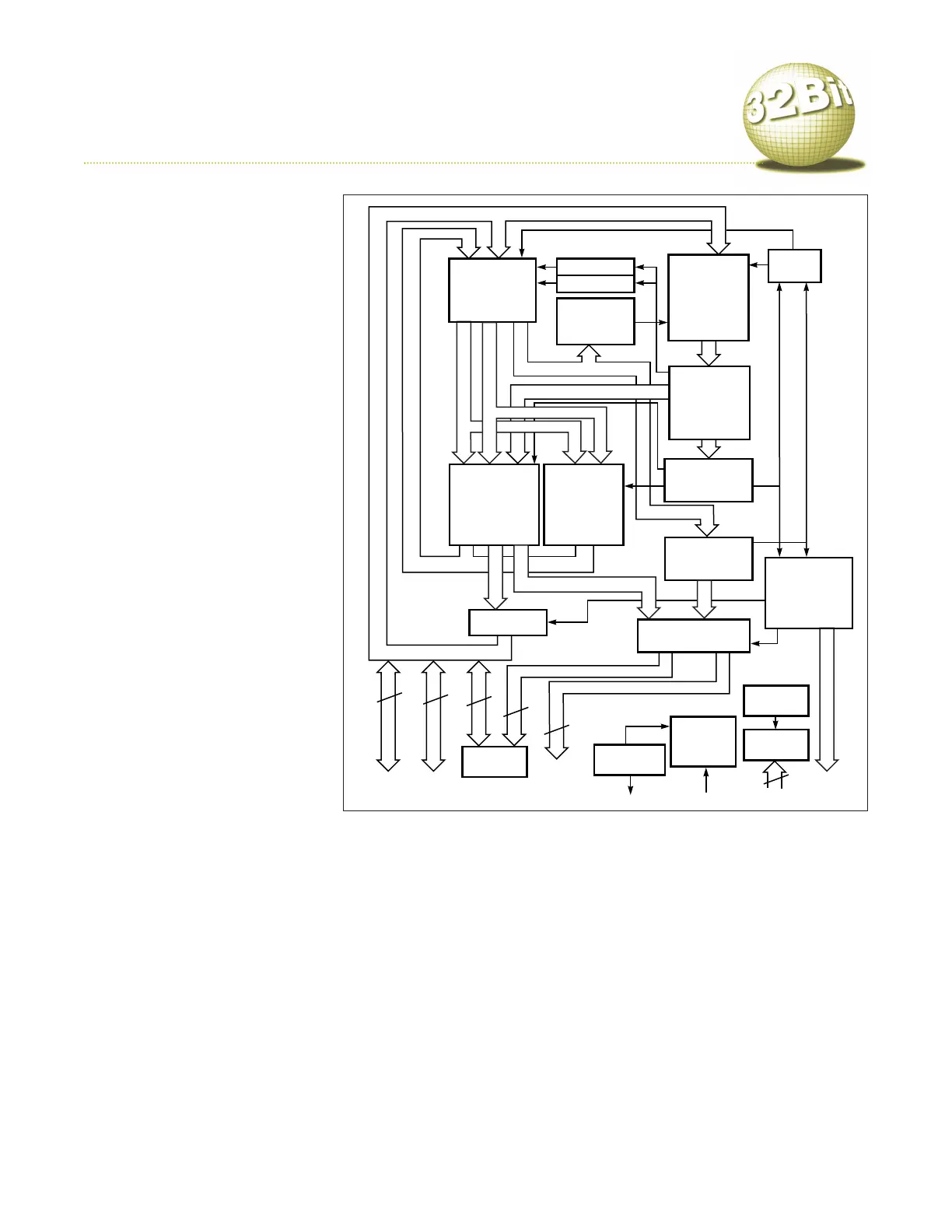

The hyperstone E1-32X combines

RISC and DSP technology in one core.

The E1-32X has a load/store architec-

ture built around a register set that

includes 64 general-purpose local and

22 global registers. Local registers are

organized into a 64-word, circular reg-

ister stack to hold function/subrou-

tine stack frames. The stack is orga-

nized into frames of as many as 16

words; the E1-32X keeps current

frames on chip and automatically

pushes the frame to off-chip memory

as the register stack fills and moves

frames back on chip as the register

stack empties. For fast parameter pass-

ing, the current stack frame can over-

lap the previous one with a variable

range. Instructions are 16, 32, or 48

bits wide. The variable-length instruc-

tions, which the E1-32X automatical-

ly prefetches, provide constants and

native addresses as large as 32 bits.

The 4-Gbyte address space divides

into four blocks; you can configure

each block individually for bus width

and timing. You can use these blocks

for glueless connection of DRAM,

extended-data-out DRAM, SRAM,

EPROM, or other memory devices,

each with its own timing and bus

width. A separate I/O-address space

also allows each I/O device to have its

own timing.

The integrated DSP unit, working in

parallel with the ALU and the

load/store unit, can perform DSP cal-

culations while the ALU is performing

loop counts, address calculations, or

load-and-store operations. The ALU

executes its instructions during the

latency cycles of DSP instructions. The DSP unit shares all the

E1-32X’

s functional blocks, including the register set; how-

ever, it provides dedicated result registers and 32- and 64-bit

hardware accumulators. The DSP unit supports 16- and 32-

bit data types.

Power management: In automatic power-down mode, only

the interrupt logic, clock, and DRAM-refresh logic remain

active. Sleep mode also disables DRAM refresh. At 3.3V

, cur-

rent consumption in power-down and sleep modes is less

than 2.5 mA and 100 mA, respectively

.

Special instr

uctions:

DSP instructions include multiply

,

complex and real multiply-accumulate, multiply-subtract,

and complex addition/subtraction. Other special instruc

-

tions include test-leading zeros.

Special on-chip peripherals: Hyperstone’

s E1-32X contains

a DRAM controller that allows you to program page size,

refresh rate, timing, and access parameters with an internal-

memor

y register. The controller supports fast-page-mode and

extended-data-out DRAMs. The mP also contains a single-

cycle-access, 8-kbyte memor

y, and an I/O- and peripheral-

interface controller. Y

ou can use this controller to set the width

and timing of the mP’

s address areas. An integrated PLL allows

you to multiply the external clock by a factor as large as 4.

Development tools:The vendor offers a development starter

kit, a PC-based development board, and the hyICE serial con

-

nector for stand-alone operation. The company also provides

an ANSI C compiler and DSP librar

y, a sour

ce- and task-level

debugger

, a multitasking real-time kernel, an assembler, a

linker, a librar

y manager

, and a profiler. Eonic Systems

(www

.eonic.com) and Etnoteam (www.etnoteam.com) pro

-

vide RTOS support. V

isual Tools (www

.etnoteam.it) offers a

JPEG embedded-image-compression/decompression librar

y

for the hyperstone E1-32X mP

. The library supports user-

defined subsampling for image quality and compression to

the desired size. Hyperstone provides speech compres

-

sion/decompression algorithms (G.726, G.729, G.723.1,

GSM 06.10) and a complete modem. GAO Resear

ch

(www

.gaoresearch.com) offers V

.22 modem code.

Second sources: LG Semicon (www

.lgsemicon.co.kr) is a

licensee.

hyperstone E1-32X

Loading...

Loading...