4-14

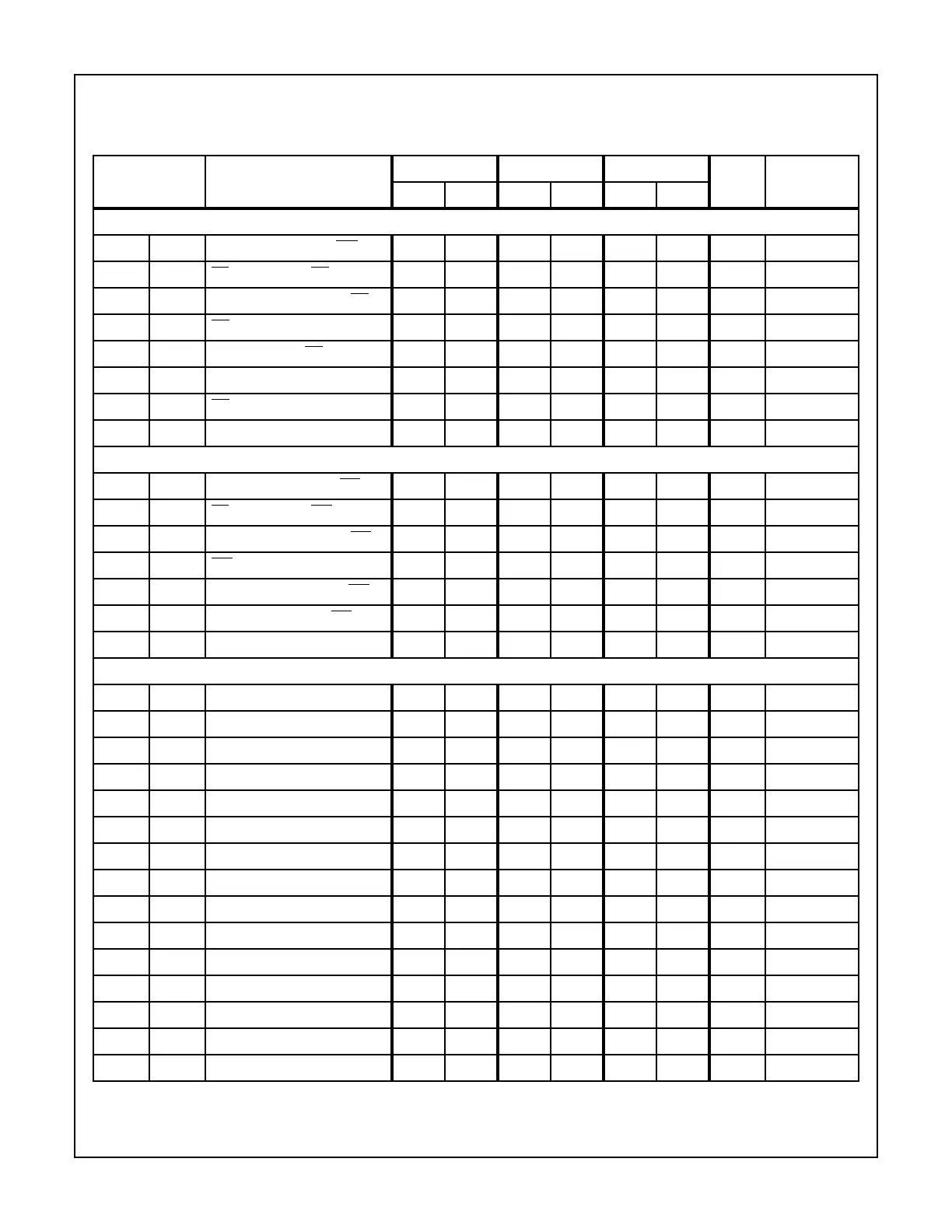

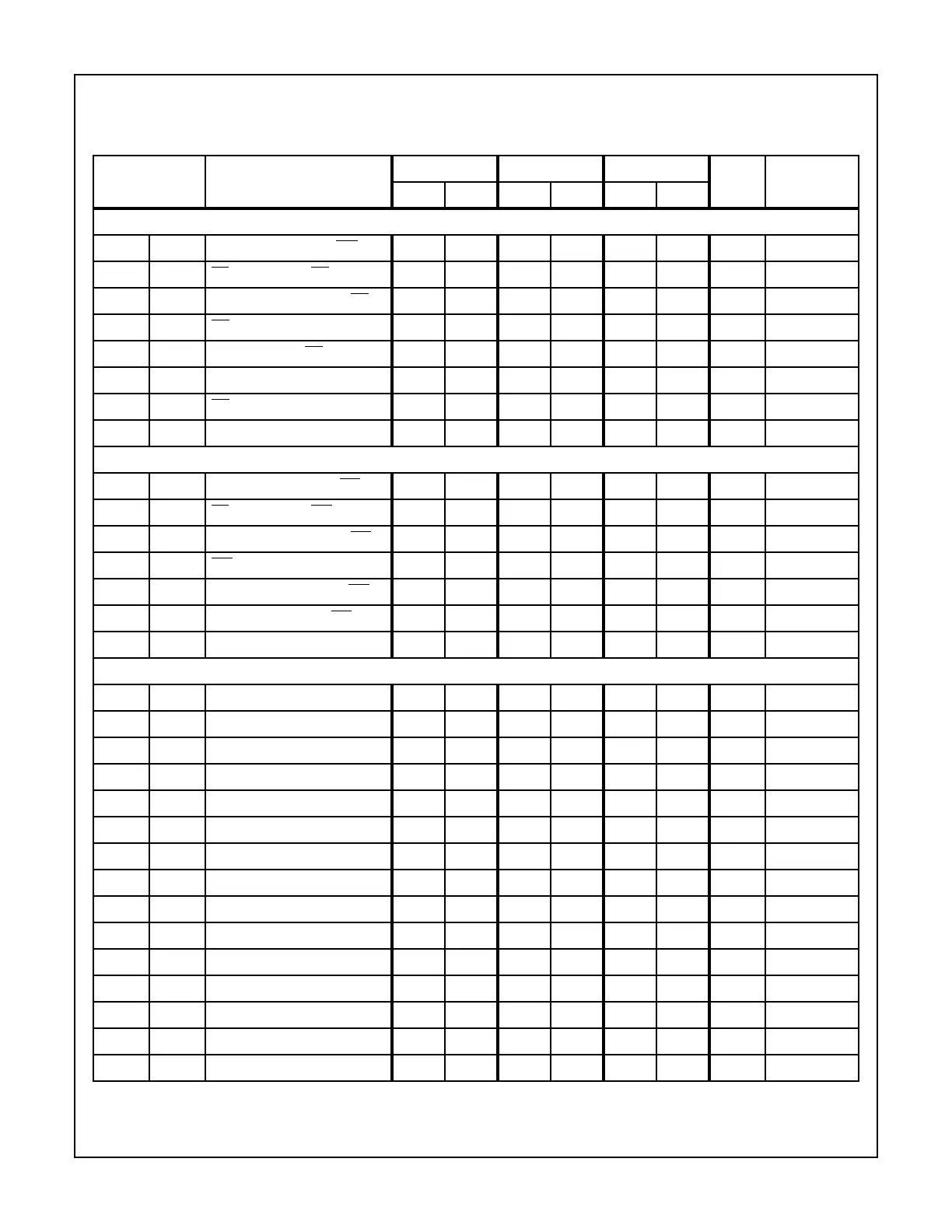

AC Electrical Specifications V

CC

= +5.0V ± 10%, T

A

= 0

o

C to +70

o

C (C82C54, C82C54-10, C82C54-12)

T

A

= -40

o

C to +85

o

C (I82C54, I82C54-10, I82C54-12)

T

A

= -55

o

C to +125

o

C (M82C54, M82C54-10, M82C54-12)

SYMBOL PARAMETER

82C54 82C54-10 82C54-12

UNITS

TEST

CONDITIONSMIN MAX MIN MAX MIN MAX

READ CYCLE

(1) TAR Address Stable Before

RD 30 - 25 - 25 - ns 1

(2) TSR CS Stable Before RD 0-0-0-ns 1

(3) TRA Address Hold Time After RD0-0-0-ns 1

(4) TRR RD Pulse Width 150 - 95 - 95 - ns 1

(5) TRD Data Delay from RD - 120 - 85 - 85 ns 1

(6) TAD Data Delay from Address - 210 - 185 - 185 ns 1

(7) TDF RD to Data Floating 5 85 5 65 5 65 ns 2, Note 1

(8) TRV Command Recovery Time 200 - 165 - 165 - ns

WRITE CYCLE

(9) TAW Address Stable Before WR 0-0-0-ns

(10) TSW CS Stable Before WR 0-0-0-ns

(11) TWA Address Hold Time After WR0-0-0-ns

(12) TWW WR Pulse Width 95 - 95 - 95 - ns

(13) TDW Data Setup Time Before WR 140 - 95 - 95 - ns

(14) TWD Data Hold Time After WR 25 - 0 - 0 - ns

(15) TRV Command Recovery Time 200 - 165 - 165 - ns

CLOCK AND GATE

(16) TCLK Clock Period 125 DC 100 DC 80 DC ns 1

(17) TPWH High Pulse Width 60 - 30 - 30 - ns 1

(18) TPWL Low Pulse Width 60 - 40 - 30 - ns 1

(19) TR Clock Rise Time - 25 - 25 - 25 ns

(20) TF Clock Fall Time - 25 - 25 - 25 ns

(21) TGW Gate Width High 50 - 50 - 50 - ns 1

(22) TGL Gate Width Low 50 - 50 - 50 - ns 1

(23) TGS Gate Setup Time to CLK 50 - 40 - 40 - ns 1

(24) TGH Gate Hold Time After CLK 50 - 50 - 50 - ns 1

(25) TOD Output Delay from CLK - 150 - 100 - 100 ns 1

(26) TODG Output Delay from Gate - 120 - 100 - 100 ns 1

(27) TWO OUT Delay from Mode Write - 260 - 240 - 240 ns 1

(28) TWC CLK Delay for Loading 0 55 0 55 0 55 ns 1

(29) TWG Gate Delay for Sampling -5 40 -5 40 -5 40 ns 1

(30) TCL CLK Setup for Count Latch -40 40 -40 40 -40 40 ns 1

NOTE:

1. Not tested, but characterized at initial design and at major process/design changes.

82C54

Loading...

Loading...