Functional Description (Continued)

2.5 Errors and Reference Voltage Adjustments

2.5.1 Zero Error

The zero of the A/D does not require adjustment. If the mini-

mum analog input voltage value, V

IN(MIN)

, is not ground, a

zero offset can be done. The converter can be made to out-

put 0000 0000 digital code for this minimum input voltage by

biasing the A/D V

IN

(−) input at this V

IN(MIN)

value (see Appli-

cations section). This utilizes the differential mode operation

of the A/D.

The zero error of the A/D converter relates to the location of

the first riser of the transfer function and can be measured by

grounding the V

IN

(−) input and applying a small magnitude

positive voltage to the V

IN

(+) input. Zero error is the differ-

ence between the actual DC input voltage that is necessary

to just cause an output digital code transition from 0000 0000

to 0000 0001 and the ideal

1

⁄

2

LSB value (

1

⁄

2

LSB

=

9.8 mV

for V

REF

/2

=

2.500 V

DC

).

2.5.2 Full-Scale

The full-scale adjustment can be made by applying a differ-

ential input voltage that is 1

1

⁄

2

LSB less than the desired ana-

log full-scale voltage range and then adjusting the magni-

tude of the V

REF

/2 input (pin 9 or the V

CC

supply if pin 9 is

not used) for a digital output code that is just changing from

1111 1110 to 1111 1111.

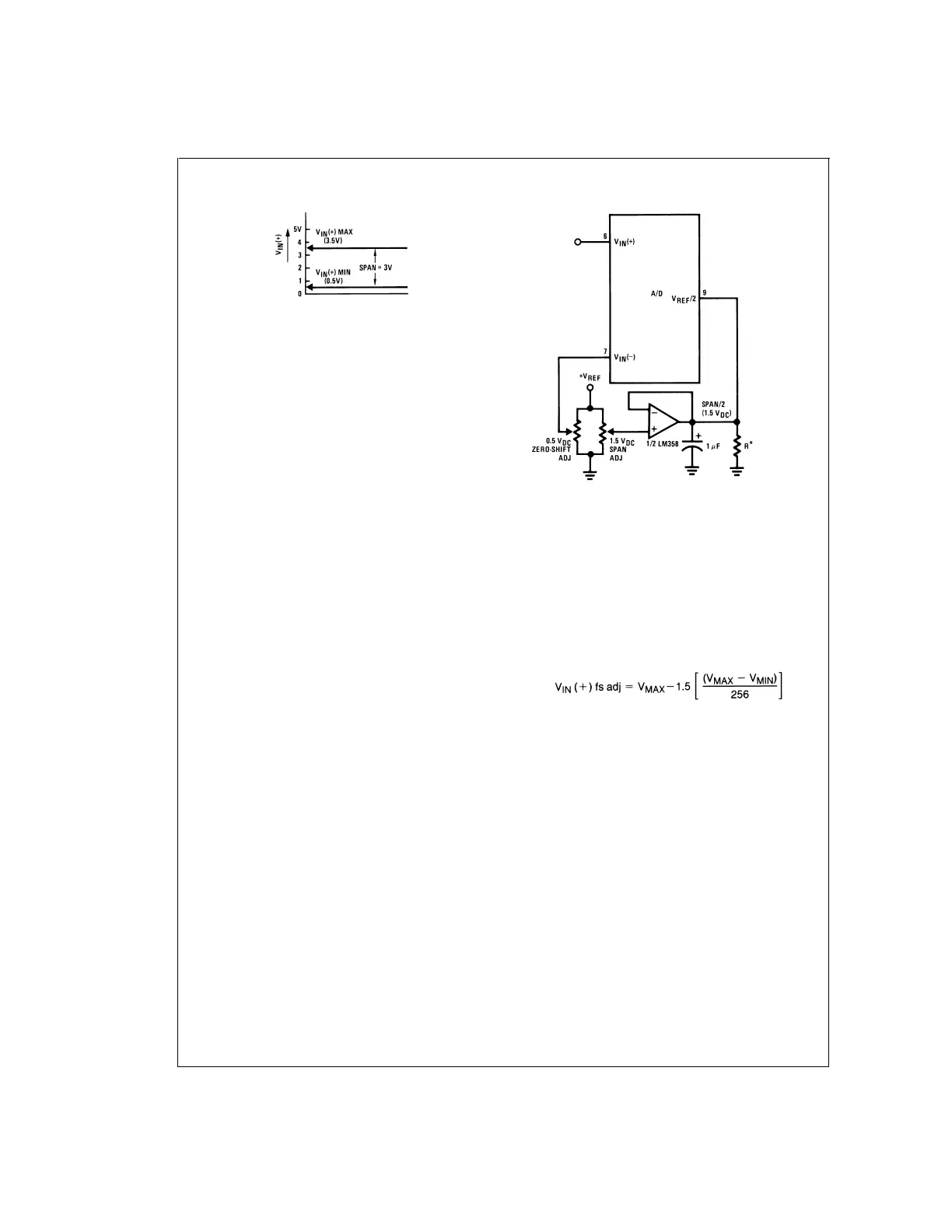

2.5.3 Adjusting for an Arbitrary Analog Input Voltage

Range

If the analog zero voltage of the A/D is shifted away from

ground (for example, to accommodate an analog input signal

that does not go to ground) this new zero reference should

be properly adjusted first. A V

IN

(+) voltage that equals this

desired zero reference plus

1

⁄

2

LSB (where the LSB is calcu-

lated for the desired analog span, 1 LSB

=

analog span/256)

is applied to pin 6 and the zero reference voltage at pin 7

should then be adjusted to just obtain the 00

HEX

to 01

HEX

code transition.

The full-scale adjustment should then be made (with the

proper V

IN

(−) voltage applied) by forcing a voltage to the

V

IN

(+) input which is given by:

where:

V

MAX

=

The high end of the analog input range

and

V

MIN

=

the low end (the offset zero) of the analog range.

(Both are ground referenced.)

The V

REF

/2 (or V

CC

) voltage is then adjusted to provide a

code change from FE

HEX

to FF

HEX

. This completes the ad-

justment procedure.

2.6 Clocking Option

The clock for the A/D can be derived from the CPU clock or

an external RC can be added to provide self-clocking. The

CLK IN (pin 4) makes use of a Schmitt trigger as shown in

Figure 8

.

DS005671-87

a) Analog Input Signal Example

DS005671-88

*

Add if V

REF

/2 ≤ 1V

DC

with LM358 to draw 3 mA to ground.

b) Accommodating an Analog Input from

0.5V (Digital Out

=

00

HEX

) to 3.5V

(Digital Out

=

FF

HEX

)

FIGURE 7. Adapting the A/D Analog Input Voltages to Match an Arbitrary Input Signal Range

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805

www.national.com 22

Loading...

Loading...