Functional Description (Continued)

4.2 Interfacing the Z-80

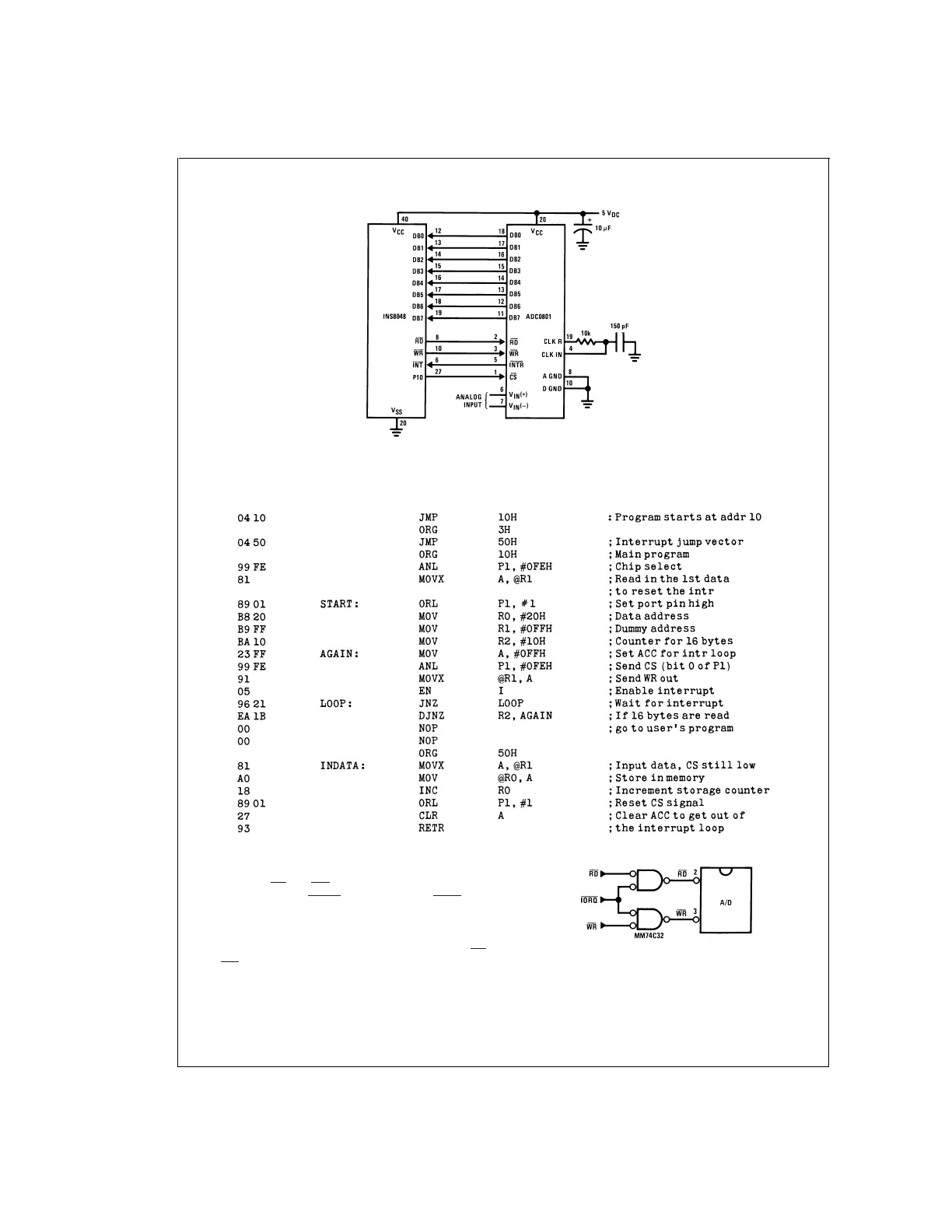

The Z-80 control bus is slightly different from that of the

8080. General RD and WR strobes are provided and sepa-

rate memory request, MREQ, and I/O request, IORQ, sig-

nals are used which have to be combined with the general-

ized strobes to provide the equivalent 8080 signals. An

advantage of operating the A/D in I/O space with the Z-80 is

that the CPU will automatically insert one wait state (the RD

and WR strobes are extended one clock period) to allow

more time for the I/O devices to respond. Logic to map the

A/D in I/O space is shown in

Figure 14

.

Additional I/O advantages exist as software DMA routines

are available and use can be made of the output data trans-

fer which exists on the upper 8 address lines (A8 toA15) dur-

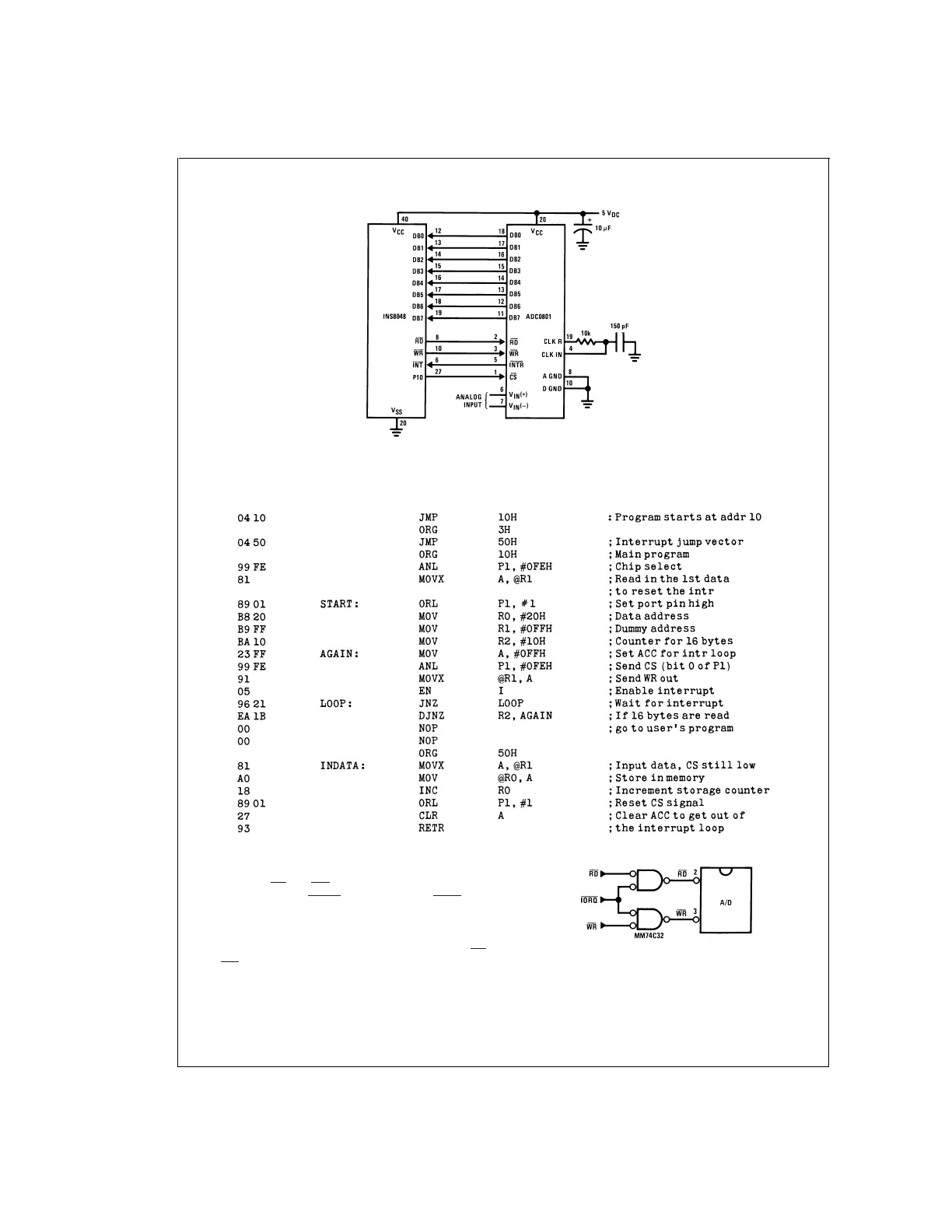

DS005671-21

FIGURE 13. INS8048 Interface

SAMPLE PROGRAM FOR

Figure 13

INS8048 INTERFACE

DS005671-A0

DS005671-23

FIGURE 14. Mapping the A/D as an I/O Device

for Use with the Z-80 CPU

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805

www.national.com 28

Loading...

Loading...