3/24/97 2-2 Architectural Overview

2.2.2 Data Memory

The XA architecture supports a 16 megabyte data memory space with a full 24-bit address. Some

derivative parts may implement fewer address lines for a smaller range. The data space

beginning at address 0 is normally on-chip and extends to the limit of the RAM size of a

particular XA derivative. For addresses above that on a derivative, the XA will automatically roll

over to external data memory.

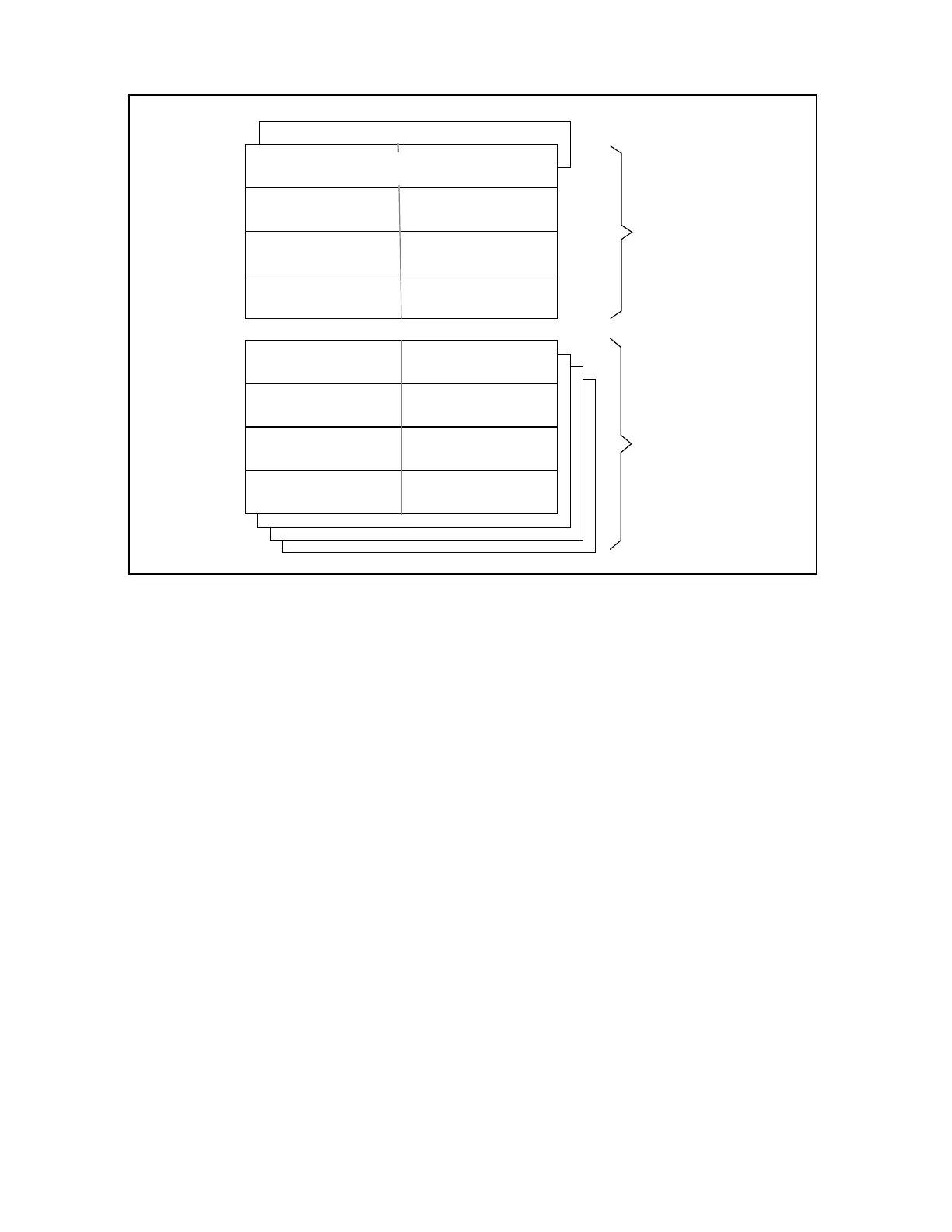

Data memory in the XA is divided into 64K byte segments (Figure 2.2) to provide an intrinsic

protection mechanism for multi-tasking systems and to improve performance. Segment registers

provide the upper 8 address bits needed to obtain a complete 24-bit address in applications that

require large data memories (Figure 2.3).

The XA provides 2 segment registers used to access data memory, the Data Segment register

(DS) and the Extra Segment register (ES). Each pointer register is associated with one of the

segment registers via the Segment Select (SSEL) register. Pointer registers retain this association

until it is changed under program control.

The XA provides flexible data addressing modes. Most arithmetic, logic, and data movement

instructions support the following modes of addressing data memory:

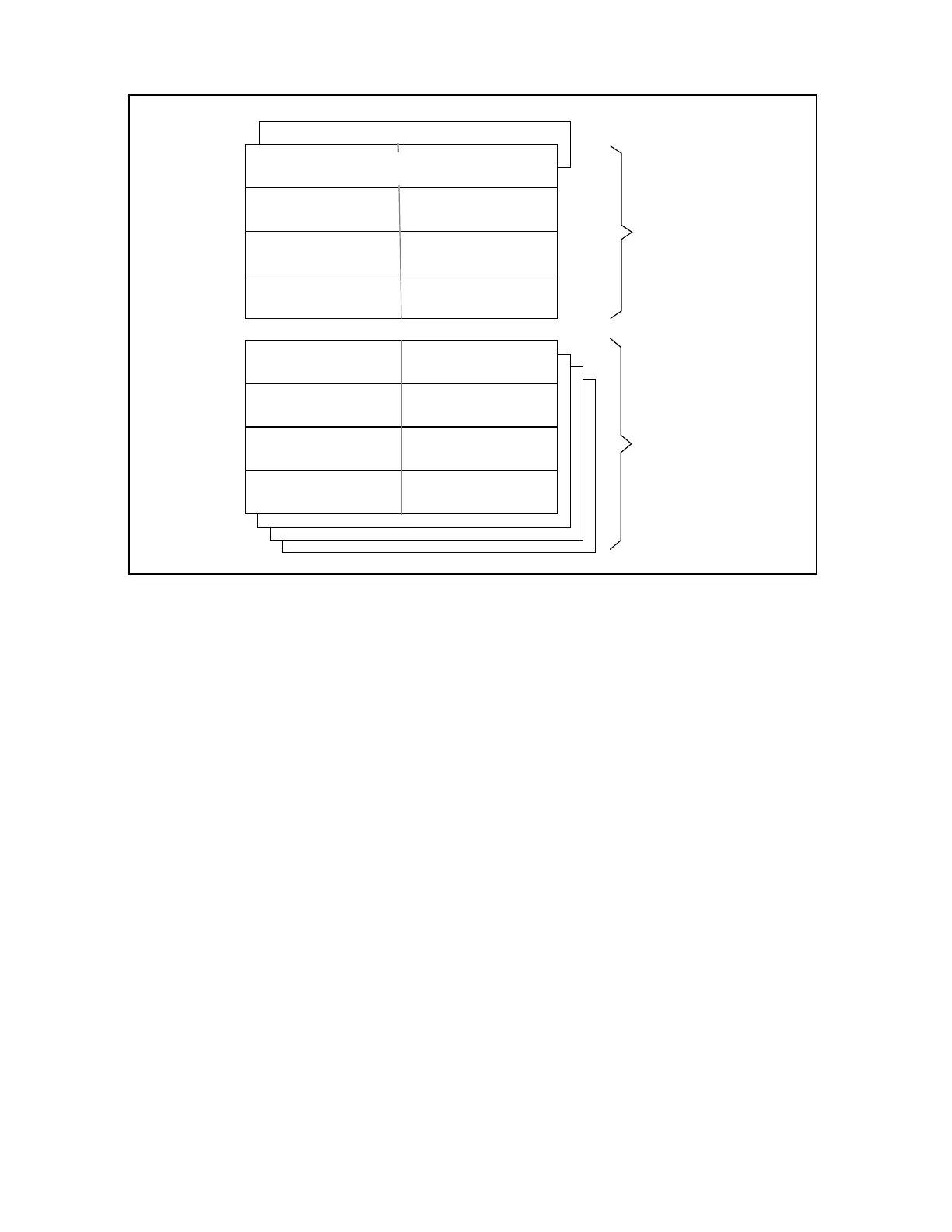

Figure 2.1 XA register file diagram

R7

R6

R5

R4

R3

R2

R1

R0

R7H

R6H

R5H

R4H

R3L

R2L

R1L

R0L

R7L

R6L

R5L

R3H

R2H

R1H

R0H

R4L

Global registers.

Banked Registers

User Stack

Pointer

System Stack Pointer

Loading...

Loading...