XA User Guide 2-21 3/24/97

2.8 Peripherals

The XA CPU core is designed to make derivative design fast and easy. Peripheral devices are not

part of the core, but are attached by means of a Special Function Register bus, called the SFR

bus, which is distinct from the CPU internal buses. So, a new XA derivative may be made by

designing a new SFR bus compatible peripheral function block, if one does not already exist,

then attaching it to the XA core.

2.9 80C51 Compatibility

The 80C51 is the most extensively designed-in 8-bit microcontroller architecture in the world,

and a vast amount of public and private code exists for this device family. For customers who

use the 80C51 or one of its derivatives, preservation of their investment in code development is

an important consideration. By permitting simple translation of source code, the XA allows

existing 80C51 code to be re-used with this higher-performance 16-bit controller. At the same

time, the XA hardware was designed with the clear goal of upward compatibility. 80C51 designs

may be migrated to the XA with very few changes necessary to software source or hardware.

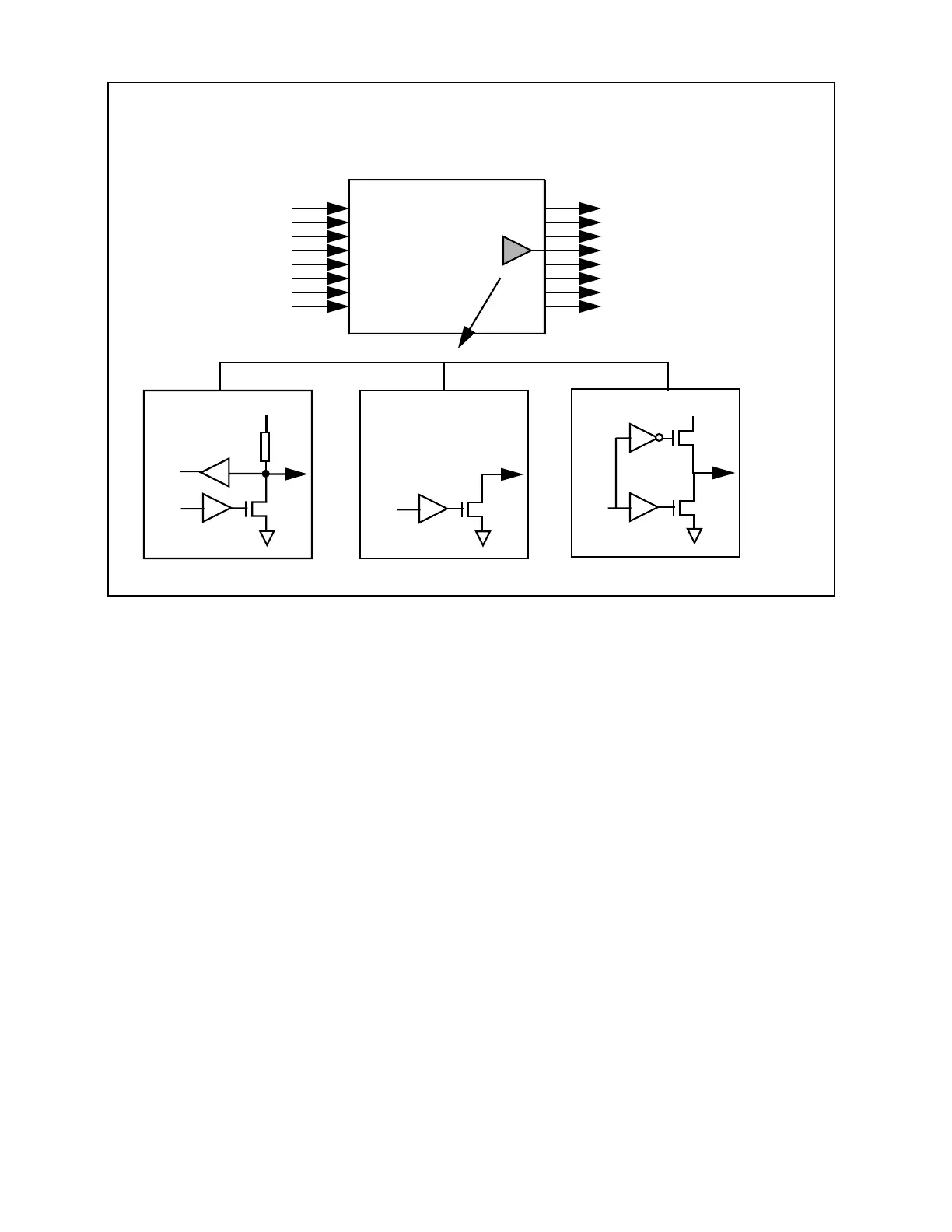

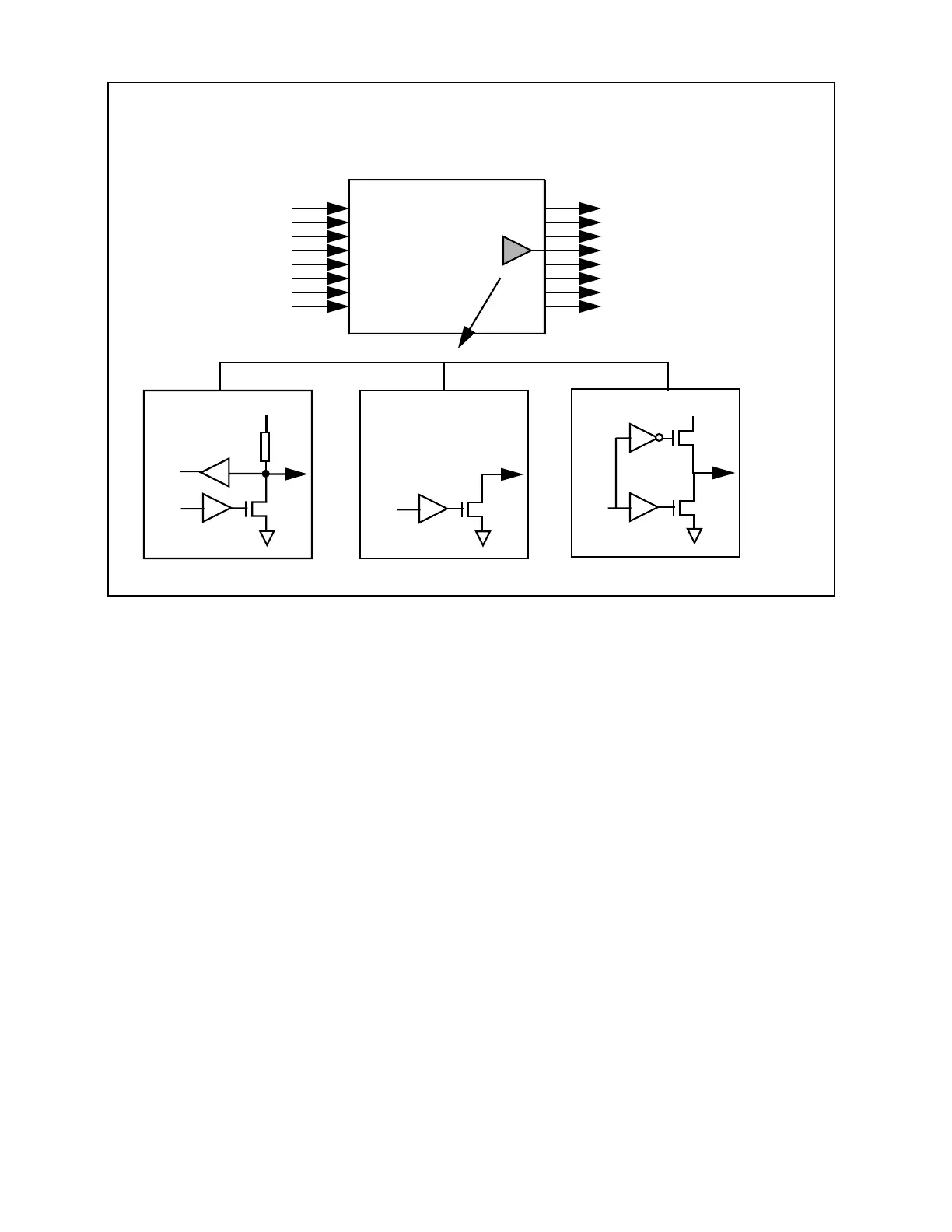

Figure 2.16 XA Port Pins with Driver Option Detail

input output

hi-Z

XA

+V

+V

R

Write

Read

Write

Write

Quasi-bidirectional

open drain push-pull

Loading...

Loading...