XA User Guide 6-4 4/17/98

6.2.3 Indirect-Offset Addressing

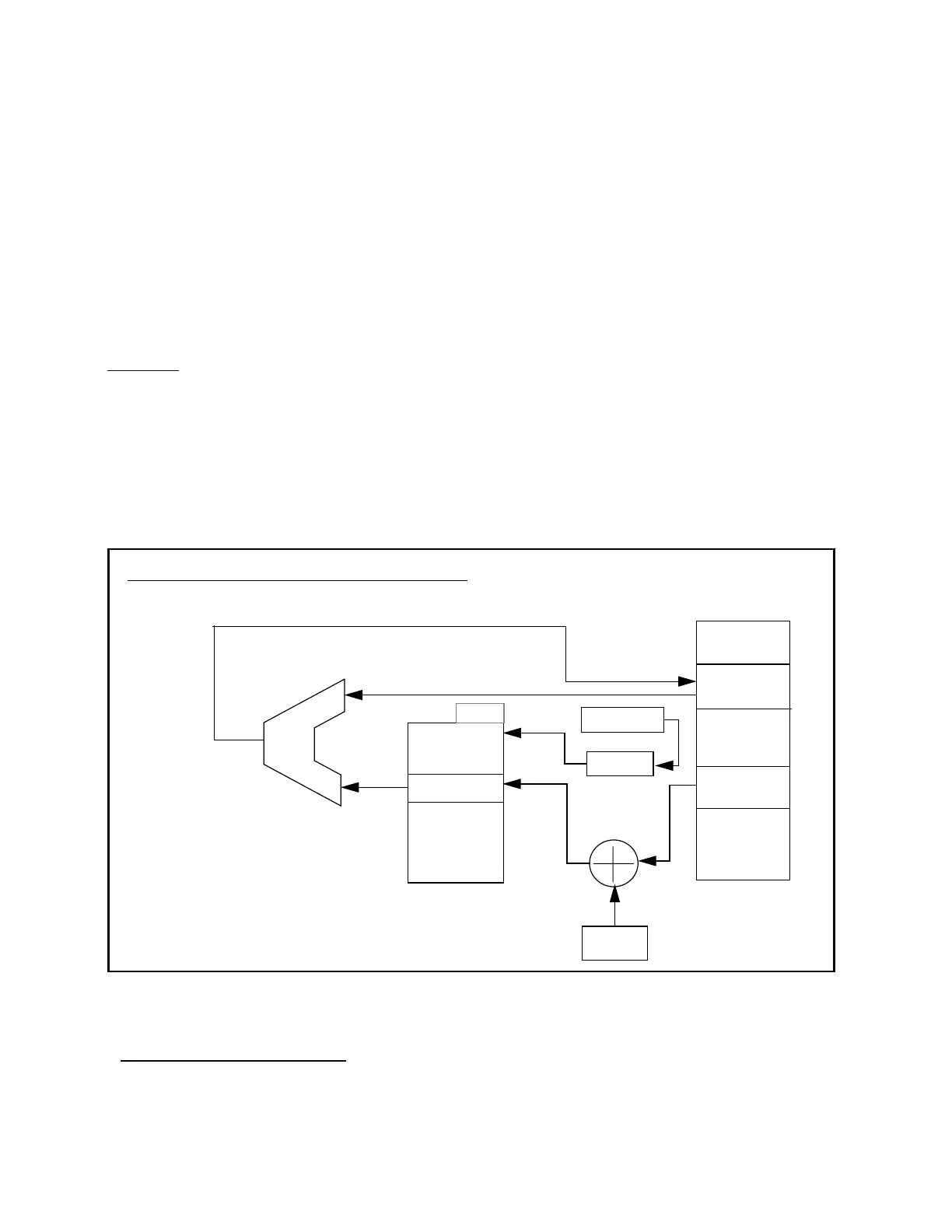

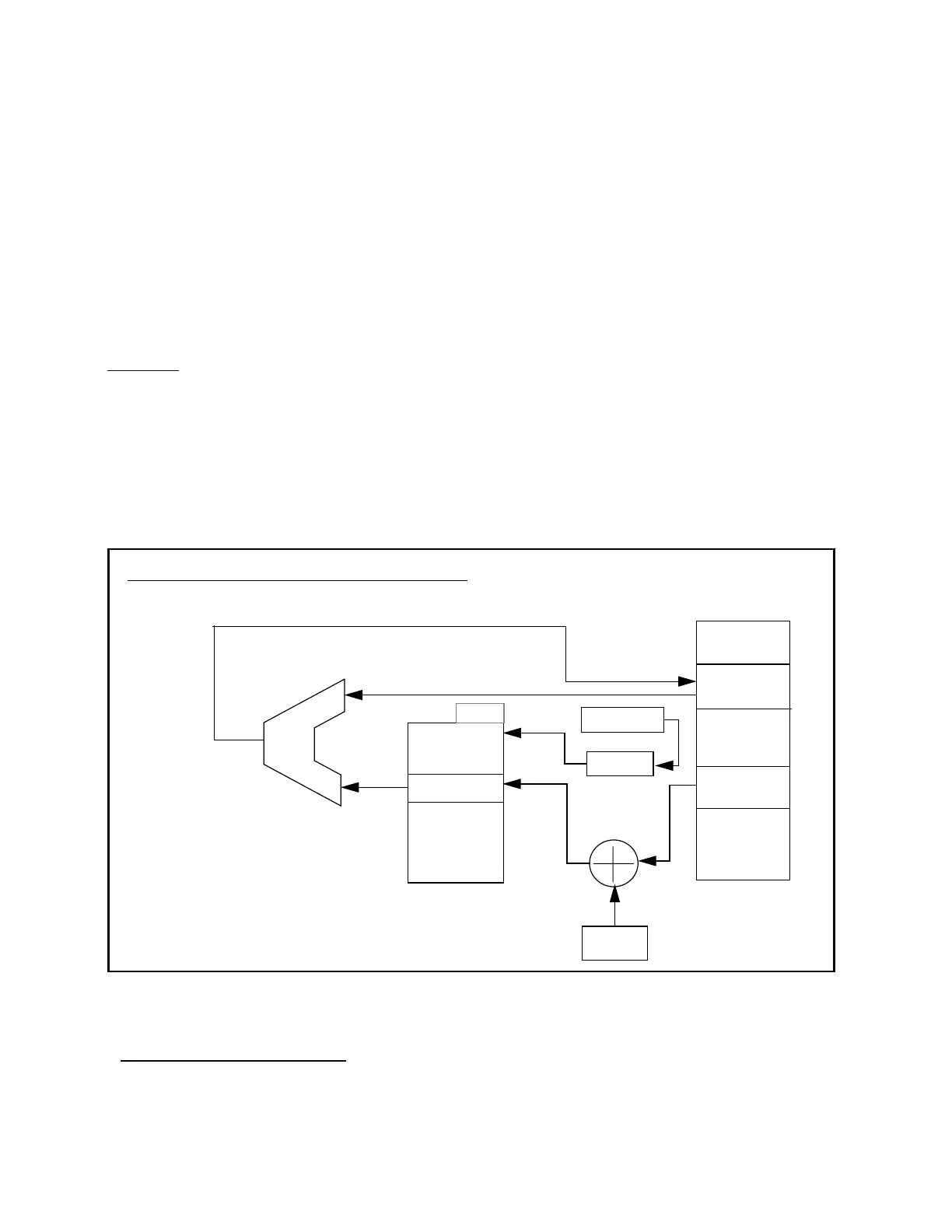

This addressing mode is just like the Register-Indirect addressing mode above except that an

additional displacement value is added to obtain the final effective address. Instructions using

this addressing mode contain a 16-bit address field and an 8 or 16-bit signed displacement field.

This field addresses 1 out of 8 pointer registers in the Register File that contains the 16-bit

address of the operand in any 64K data segment. The contents of the pointer register are added to

the signed displacement to obtain the effective address

3

(which must be even) of the operand.

For data the segment is identified by the 8-bit contents of DS or the ES and for code, by the 8-bit

contents of PC23-16 or CS as selected by the appropriate bit (SSEL.bit n = 0 selects DS and 1

selects ES for data and SSEL.bitn = 0 selects PC and 1 selects CS for code) in the segment select

register SSEL.

Example: ADD R5, [R3 +30h] Before: R3 contains C000h

SSEL.3 = 1 R5 contains 0065h

i.e., the operand is in Word at C030h = A540h

segment determined

by the contents of ES After: R3 contains C000h

So, if ES = 04, the R5 contains A5A5h

operand is in segment Word at C030h = A540h

4 of data memory.

Figure 6.3

3. In case of an odd address, the XA forces the operand fetch from the next lower even boundary

(address.bit0 = 0)

ALU

ADD R5, [R3+30]

0h

DATA MEMORY

REGISTER - INDIRECT WITH OFFSET

REGISTER FILE

C000h

DESTINATION

FFFFh

R5

POINTER

SSEL.3 = 1

ES = 4

Seg4

R3

0065h A5A5h

0030h

C030h

A540h

Loading...

Loading...