4/17/98 6-7 Addressing Modes and Data Types

6.2.7 Bit Addressing

Instructions using the bit addressing mode contain a 10-bit field containing the address of the bit

operand. The XA supports three bit address spaces, which are encoded into the same format. The

spaces are: 256 bits in the register file (the entire active register file); 256 bits in the data memory

(byte addresses 20 through 3F hex on the current data segment); and 512 bits in the SFR space (byte

addresses 400 through 43F hex).

Bit addresses 0 to FF hex map to the register file, bit addresses 100 to 1FF hex map to data memory,

and bit addresses 200 to 3FF map to the SFR space.

A separate bit-addressable space (20-3F hex) in the direct-address data memory, exists for each

segment. The current working segment for the direct-address space being always identified by the

DS register.

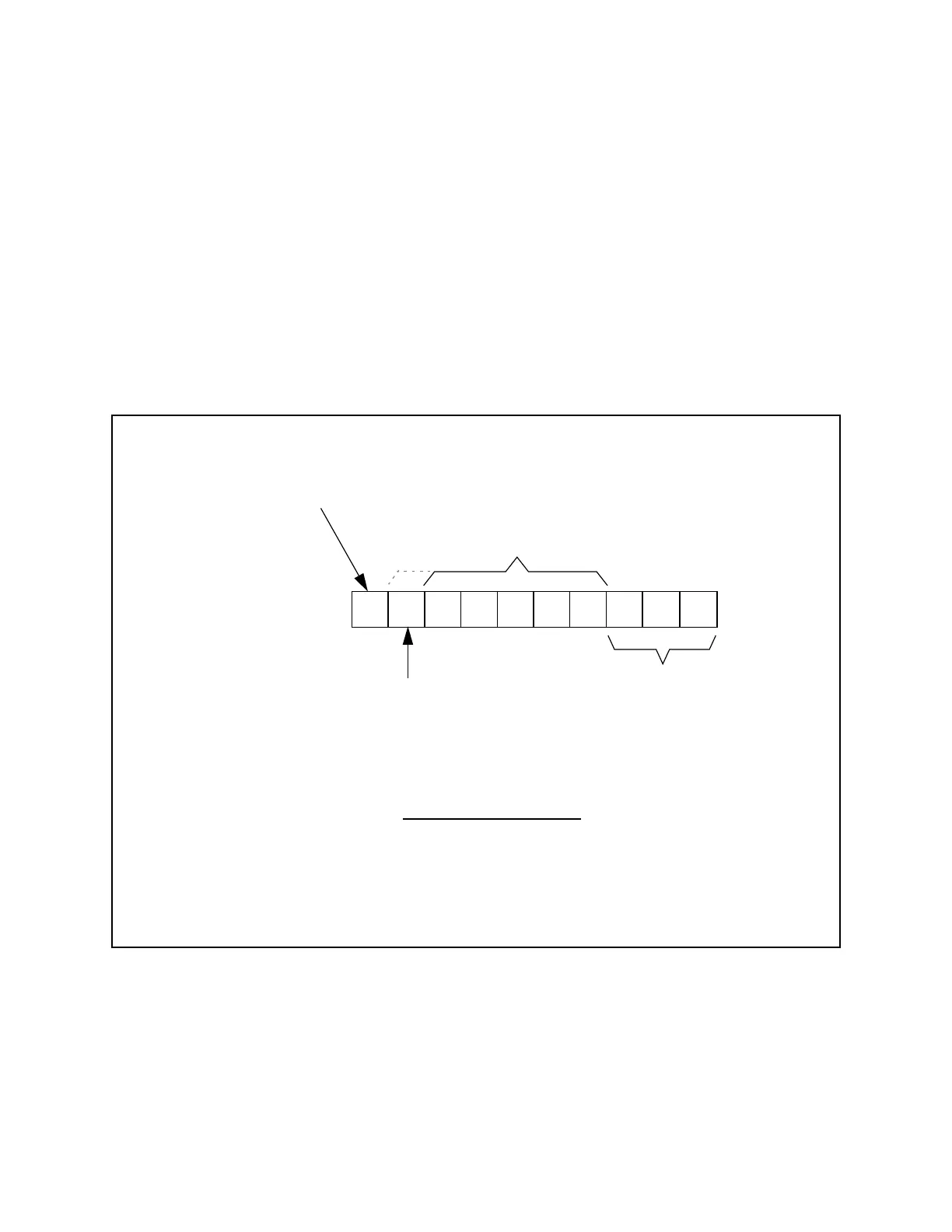

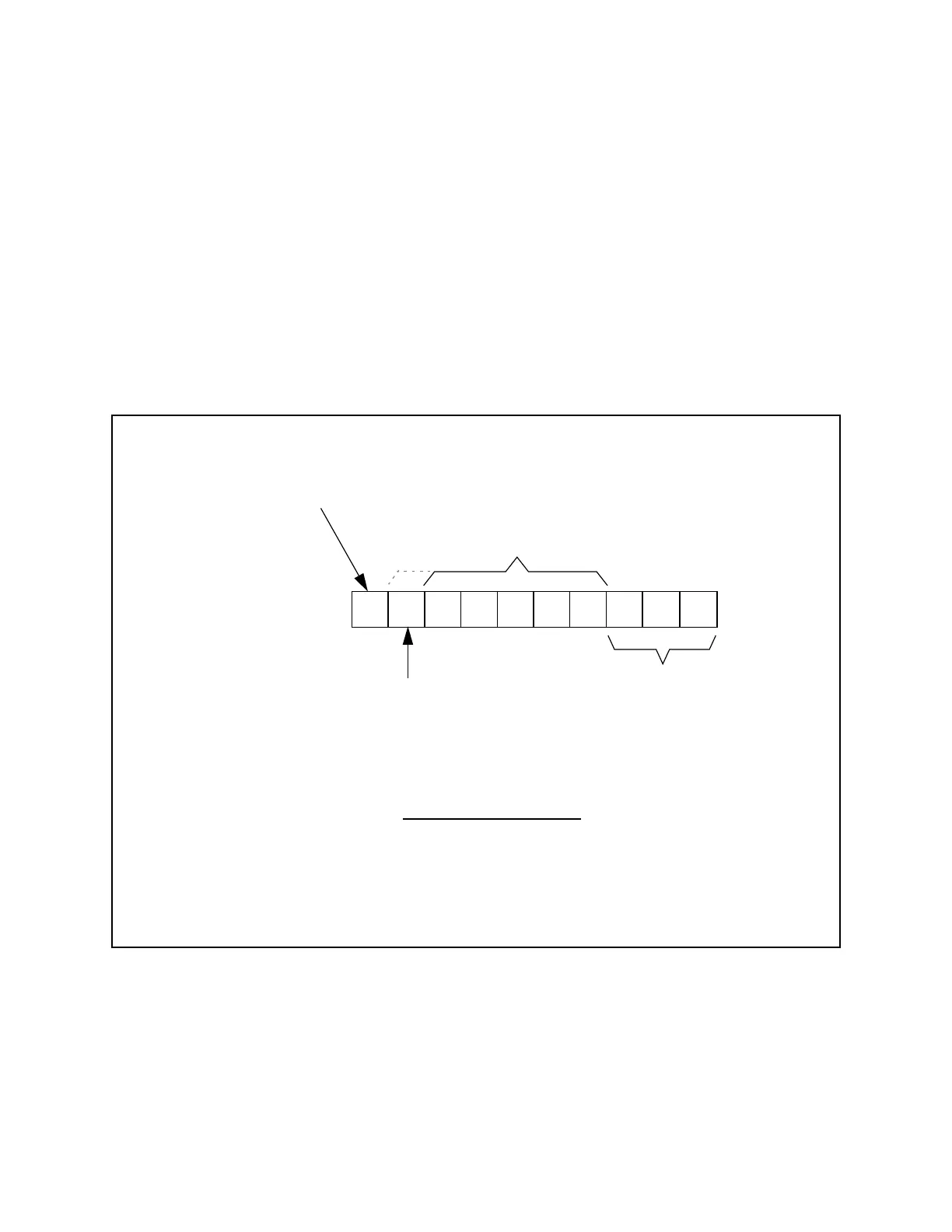

The encoding of the 10-bit field for bit addresses is as follows:

Figure 6.6

3-bit field identifies 1 of

8 bits in a byte.

This bit determines whether

the bit address is an SFR or

not (1 = SFR).

If not an SFR bit address, this bit

determines whether the bit address

is in the Register File or the data

memory (0 = Register file, 1 =

data memory).

5 or 6 bit field (6 bits

for an SFR) identifies

the byte that the

addressed bit resides

in.

Bit Address Encoding

9 8 7 6 5 4 3 2 1 0

Examples:

For a given data segment,

1 001100 010 = Bit 2 of an SFR at address 0Ch (i.e., 40Ch in the map)

0 001100 010 = Bit 2 of Register file at address 0Ch, i.e., R6L

0 101100 010 = Bit 2 of Data memory address 0Ch

Loading...

Loading...