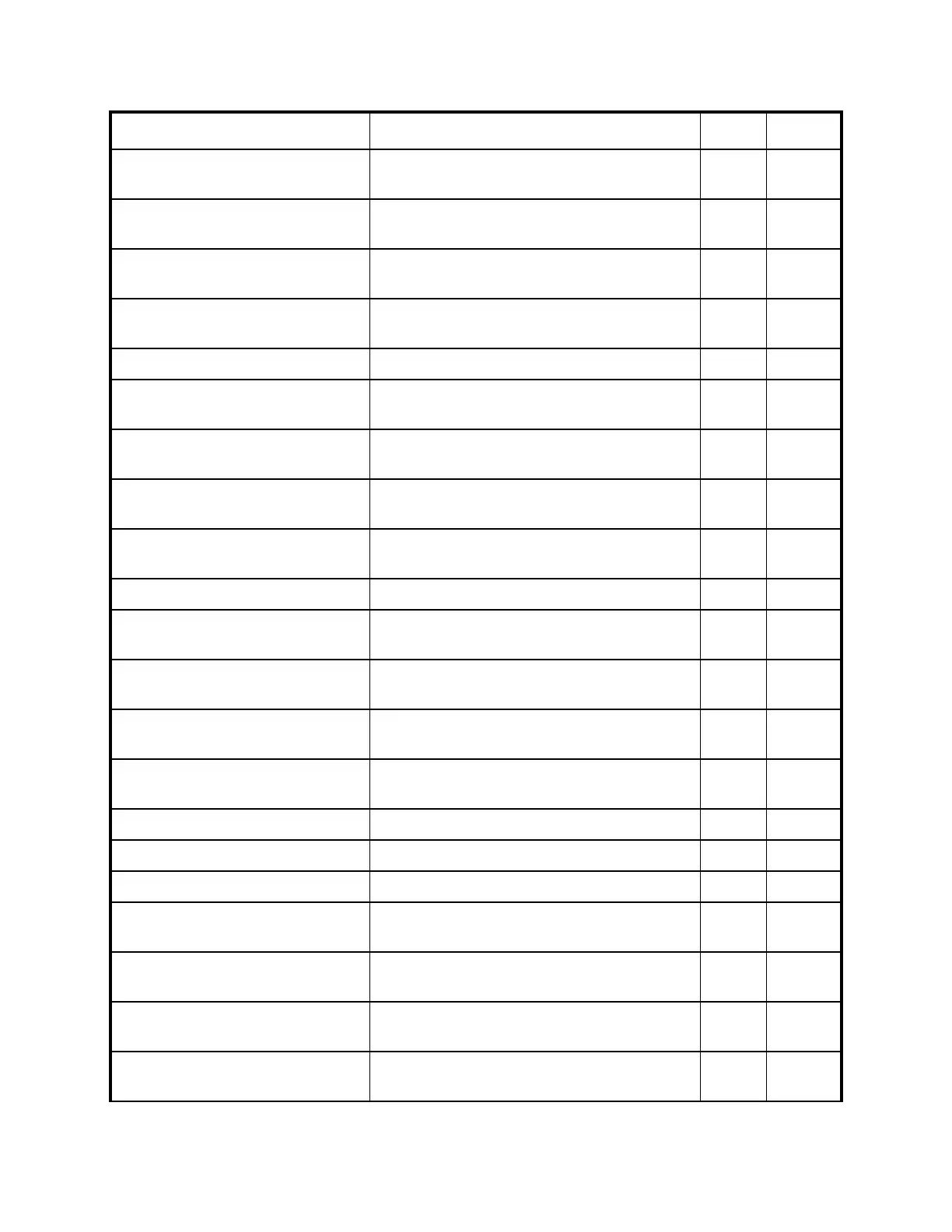

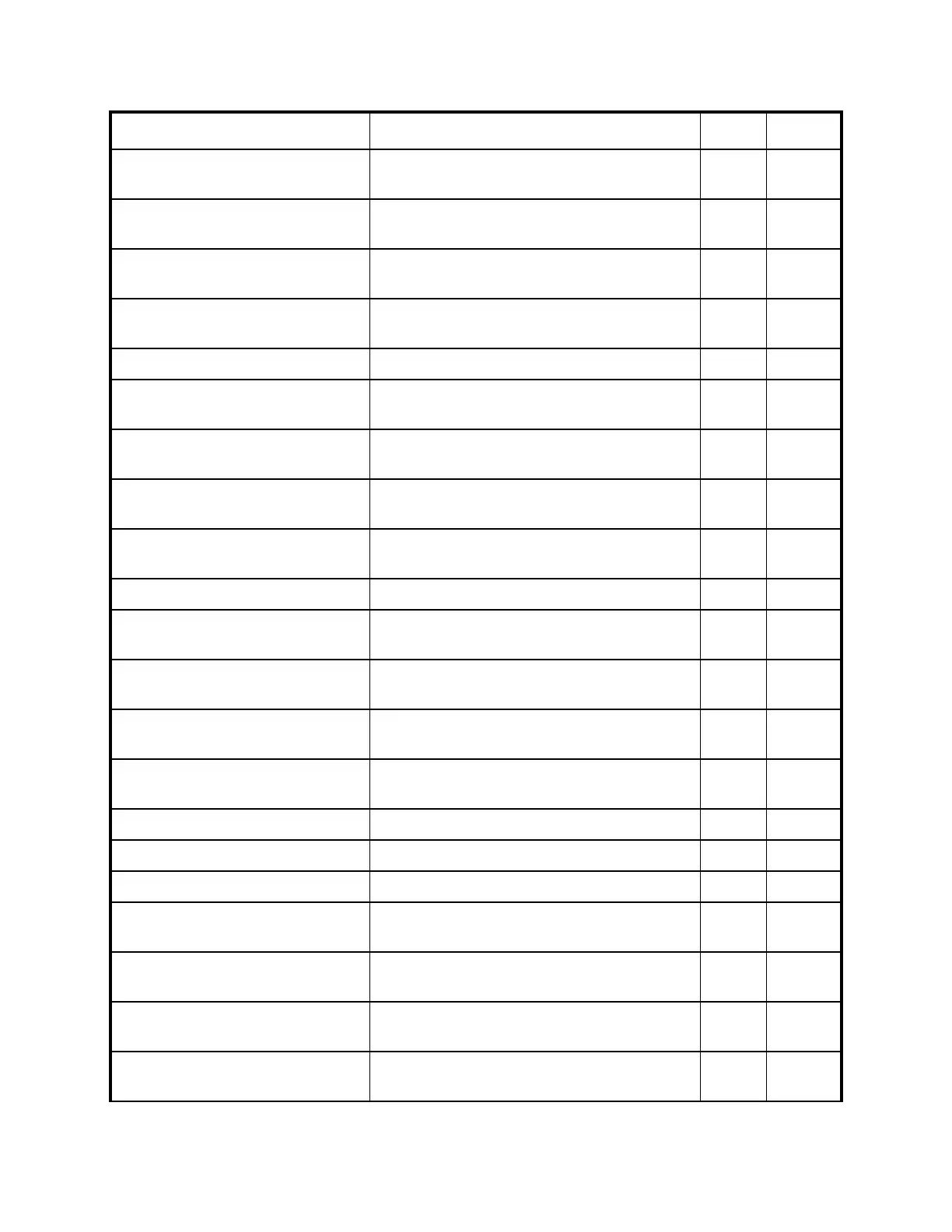

4/17/98 6-19 Addressing Modes and Data Types

ADDC [Rd+offset16], #data8 Add 8-bit immediate data to register-indirect

with 16-bit offset and carry

56

ADDC [Rd+offset16], #data16 Add 16-bit immediate data to register-indirect

with 16-bit offset and carry

66

ADDC direct, #data8 Add 8-bit immediate data to memory with

carry

44

ADDC direct, #data16 Add 16-bit immediate data to memory with

carry

54

ADDS Rd, #data4 Add 4-bit signed immediate data to register 2 3

ADDS [Rd], #data4 Add 4-bit signed immediate data to register-

indirect

24

ADDS [Rd+], #data4 Add 4-bit signed immediate data to register-

indirect with auto-increment

25

ADDS [Rd+offset8], #data4 Add register-indirect with 8-bit offset to 4-bit

signed immediate data

36

ADDS [Rd+offset16], #data4 Add register-indirect with 16-bit offset to 4-bit

signed immediate data

46

ADDS direct, #data4 Add 4-bit signed immediate data to memory 3 4

ASL Rd, Rs Logical left shift destination register by the

value in the source register

2 See

Note1

ASL Rd, #data4 Logical left shift register by the 4-bit

immediate value

2 See

Note1

ASR Rd, Rs Arithmetic shift right destination register by

the count in the source

2 See

Note1

ASR Rd, #data4 Arithmetic shift right register by the 4-bit

immediate count

2 See

Note1

CMP Rd, Rs Compare destination and source registers 2 3

CMP [Rd], Rs Compare register with register-indirect 2 4

CMP Rd, [Rs] Compare register-indirect with register 2 4

CMP [Rd+offset8], Rs Compare register with register-indirect with 8-

bit offset

36

CMP [Rd+offset16], Rs Compare register with register-indirect with

16-bit offset

46

CMP Rd, [Rs+offset8] Compare register-indirect with 8-bit offset

with register

36

CMP Rd,[Rs+offset16] Compare register-indirect with 16-bit offset

with register

46

Table 6.5

Mnemonic Description Bytes Clocks

Loading...

Loading...