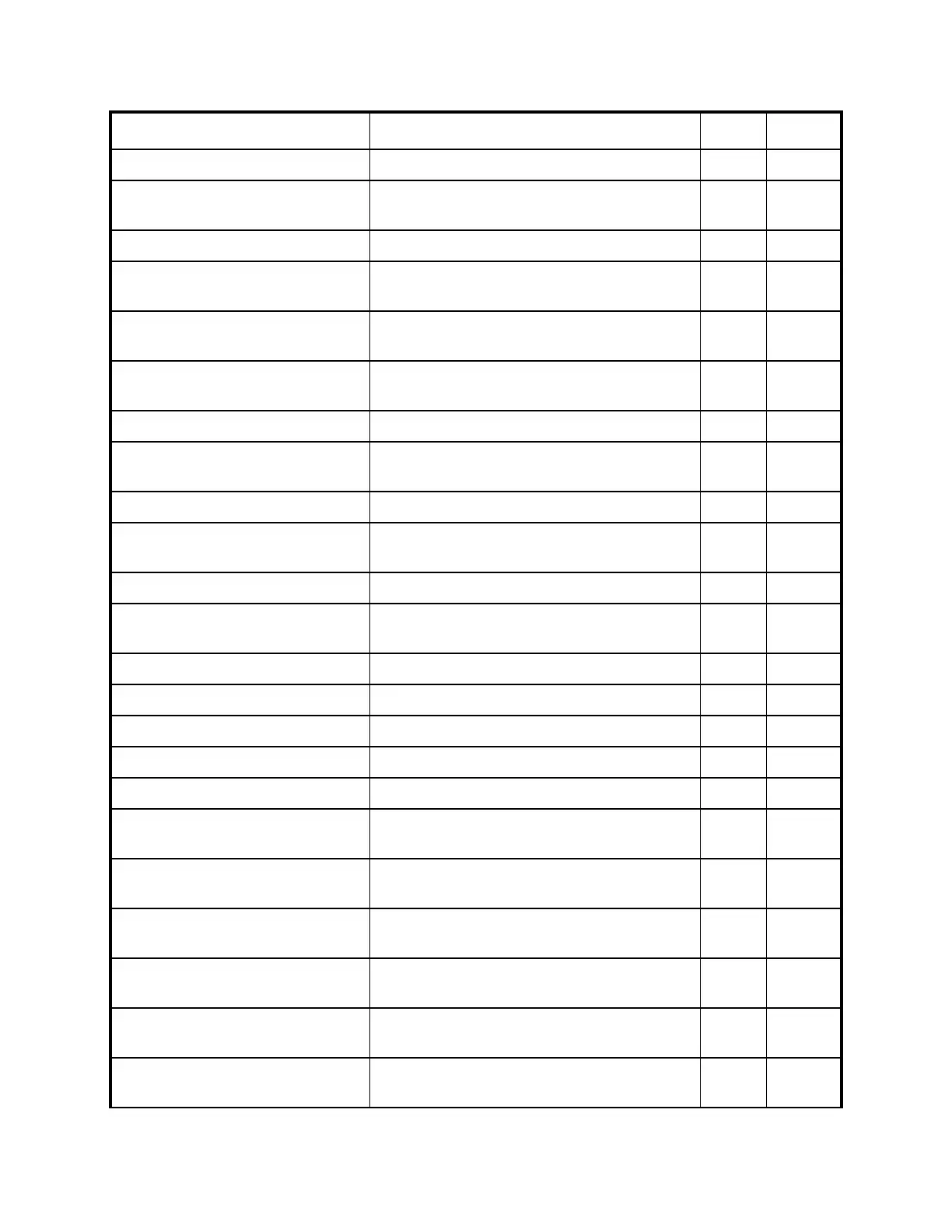

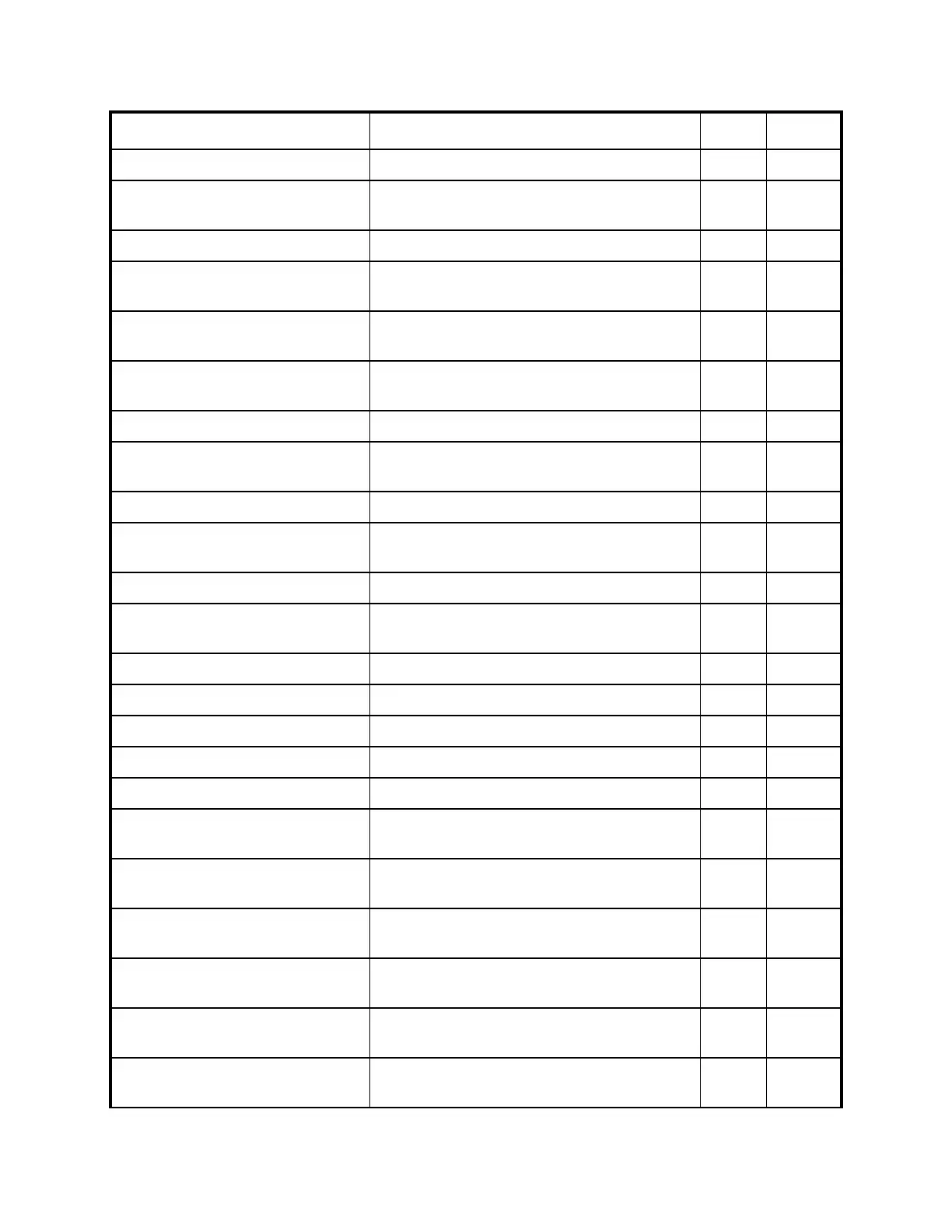

4/17/98 6-21 Addressing Modes and Data Types

DIVU.w Rd, Rs 16X8 unsigned register divide 2 12

DIVU.w Rd, #data8 16X8 unsigned register divide with immediate

byte

312

DIVU.d Rd, Rs 32X16 unsigned double register divide 2 22

DIVU.d Rd, #data16 32X16 unsigned double register divide with

immediate word

422

LEA Rd, Rs+offset8 Load 16-bit effective address with 8-bit offset

to register

33

LEA Rd, Rs+offset16 Load 16-bit effective address with 16-bit

offset to register

43

MUL.w Rd, Rs 16X16 signed multiply of register contents 2 12

MUL.w Rd, #data16 16X16 signed multiply 16-bit immediate data

with register

412

MULU.b Rd, Rs 8X8 unsigned multiply of register contents 2 12

MULU.b Rd, #data8 8X8 unsigned multiply of 8-bit immediate data

with register

312

MULU.w Rd, Rs 16X16 unsigned register multiply 2 12

MULU.w Rd, #data16 16X16 unsigned multiply 16-bit immediate

data with register

412

NEG Rd Negate (twos complement) register 2 3

SEXT Rd Sign extend last operation to register 2 3

SUB Rd, Rs Subtract registers direct 2 3

SUB Rd, [Rs] Subtract register-indirect to register 2 4

SUB [Rd], Rs Subtract register to register-indirect 2 4

SUB Rd, [Rs+offset8] Subtract register-indirect with 8-bit offset to

register

36

SUB [Rd+offset8], Rs Subtract register to register-indirect with 8-bit

offset

36

SUB Rd, [Rs+offset16] Subtract register-indirect with 16-bit offset to

register

46

SUB [Rd+offset16], Rs Subtract register to register-indirect with 16-

bit offset

46

SUB Rd, [Rs+] Subtract register-indirect with auto increment

to register

25

SUB [Rd+], Rs Subtract register-indirect with auto increment

to register

25

Table 6.5

Mnemonic Description Bytes Clocks

Loading...

Loading...