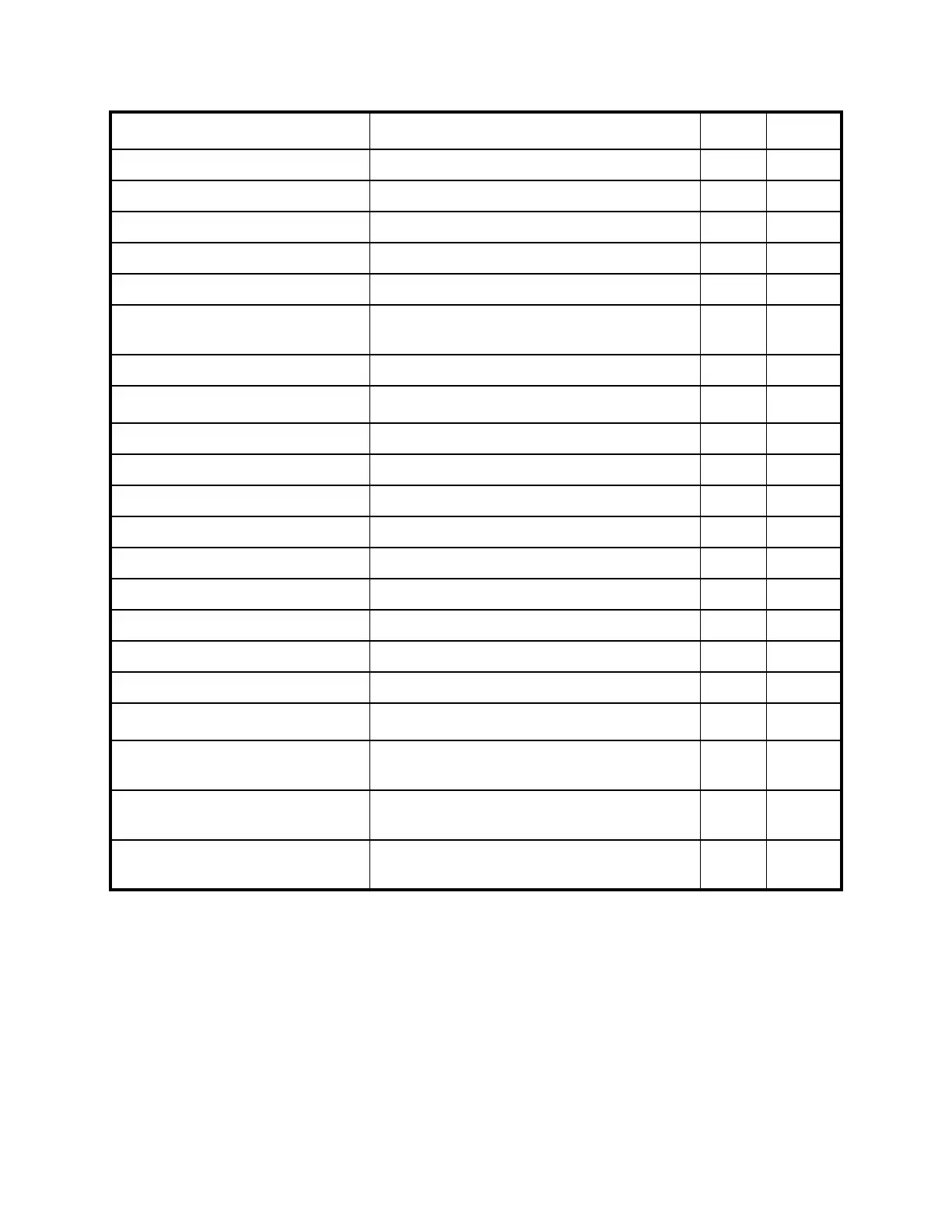

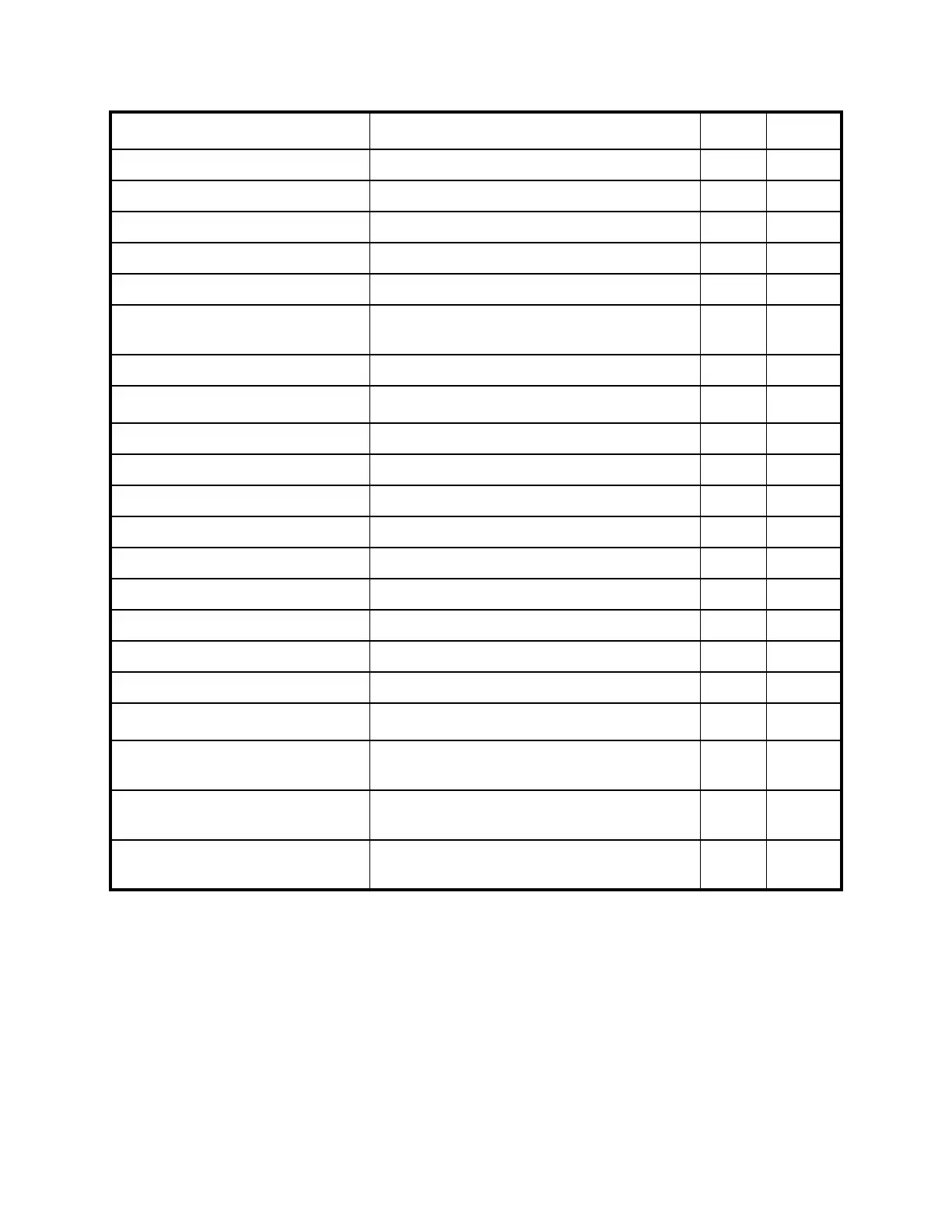

4/17/98 6-31 Addressing Modes and Data Types

Note 1: For 8 and 16 bit shifts, it is 4+1 per additional two bits. For 32-bit shifts, it is 6+1 per additional two bits.

Note 2: 3 clocks per register pushed.

Note 3: 4 clocks for the first register and two clocks for each additional register.

JNB bit,rel8 Jump if bit not set 4 10t/6nt

JNZ rel8 Jump if accumulator not equal zero 2 6t/3nt

JZ rel8 Jump if accumulator equals zero 2 6t/3nt

NOP No operation 1 3

RET Return from subroutine 2 8/6(PZ)

RETI Return from interrupt 2 10/

8(PZ)

Bit Manipulation

ANL C, bit Logical AND bit to carry 3 4

ANL C, /bit Logical AND complement of a bit to carry 3 4

CLR bit Clear bit 3 4

MOV C, bit Move bit to the carry flag 3 4

MOV bit, C Move carry to bit 3 4

ORL C, bit Logical OR a bit to carry 3 4

ORL C, /bit Logical OR complement of a bit to carry 3 4

SETB bit Sets the bit specified 3 4

Exception / Trap

BKPT Cause the breakpoint trap to be executed. 1 23/

19(PZ)

RESET Causes a hardware Reset, identical to an

external Reset

218

TRAP #data4 Causes 1 of 16 hardware traps to be

executed

2 23/

19(PZ)

Table 6.5

Mnemonic Description Bytes Clocks

Loading...

Loading...