3/24/97 9-7 8051 Compatibility

In this case, the translated code actually changed very little. Primarily, the 80C51 register names

have been replaced by the new ones reserved for them in the XA. The increment (INC)

instruction became a short add (ADDS), and the mnemonic for multiply (MUL) changed to

MULU8.

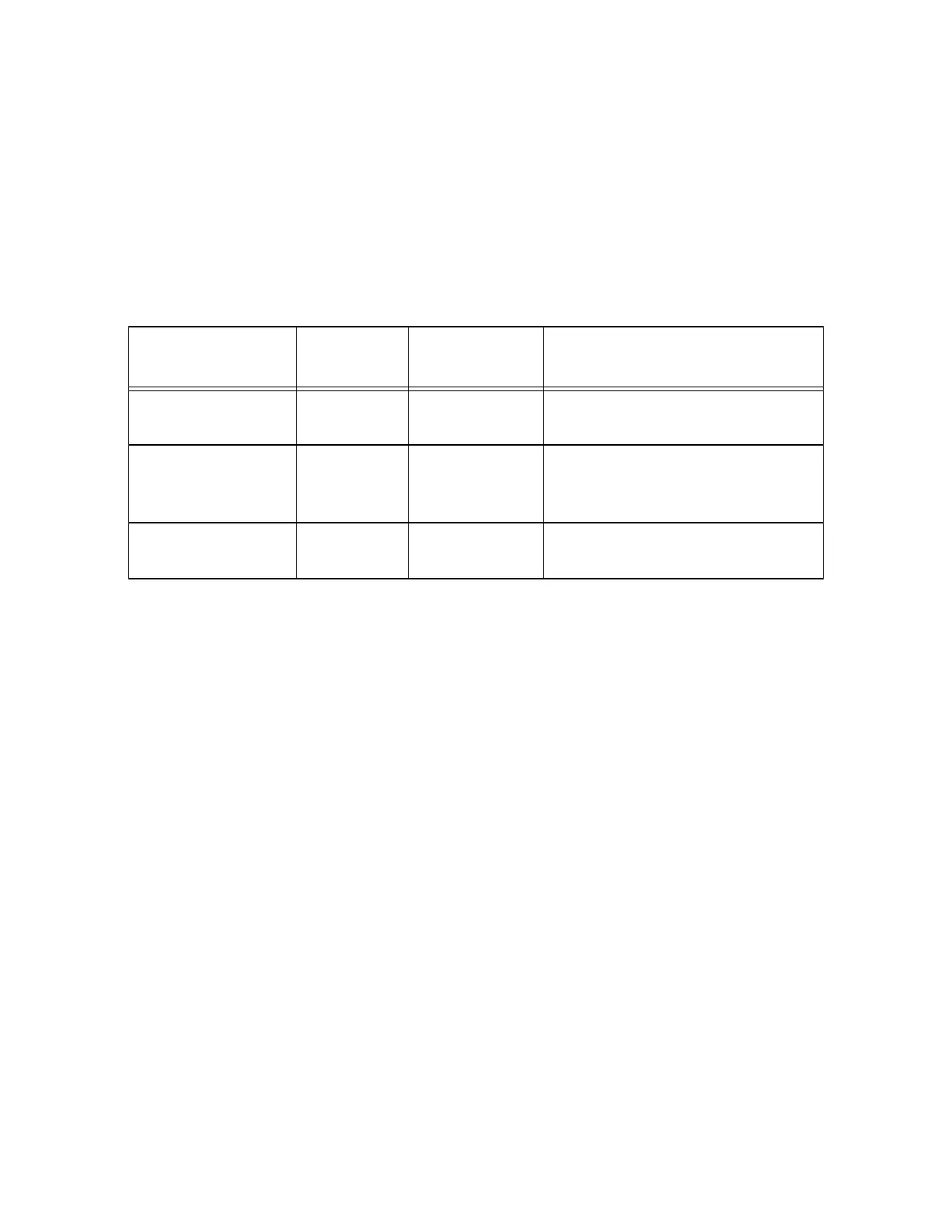

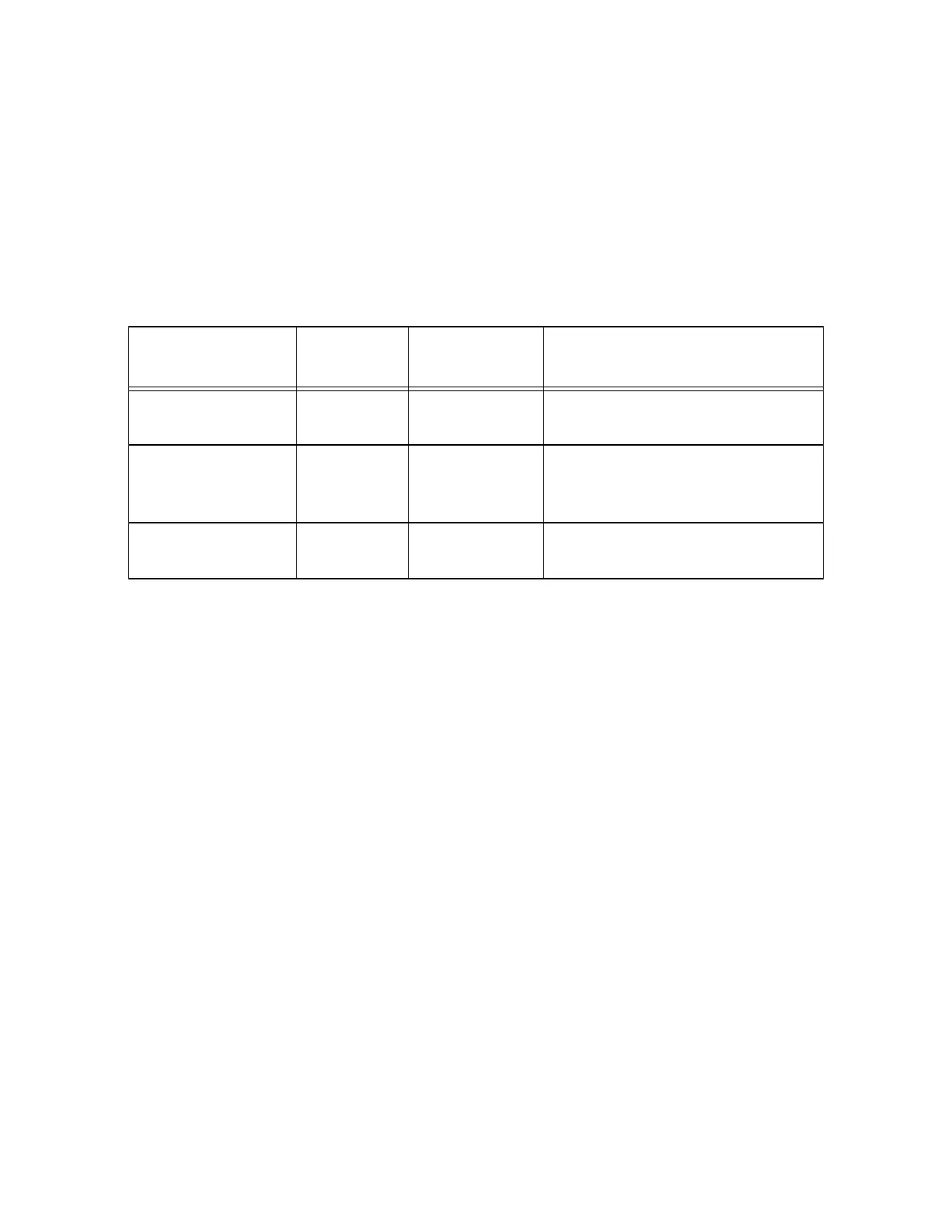

Some basic statistical information about these code samples may be found in table 9.1. These

statistics show a large performance increase for the XA code. This is significant because the code

is only simple translated 80C51 code and therefore does not take any advantage of the XA’s

unique features.

Table 9.1: 80C51 to XA Code Translation Statistics

Statistic

80C51

code

XA

translation

Comments

Code bytes 28 40 - one NOP added for branch

alignment on XA

Clocks to execute 300 78 - includes XA pre-fetch queue

analysis, raw execution is 66

clocks

Time to execute

@ 20MHz

15 µsec 3.9 µsec - a nearly 4x improvement

without any optimization

Loading...

Loading...