4-2

Functional Diagram

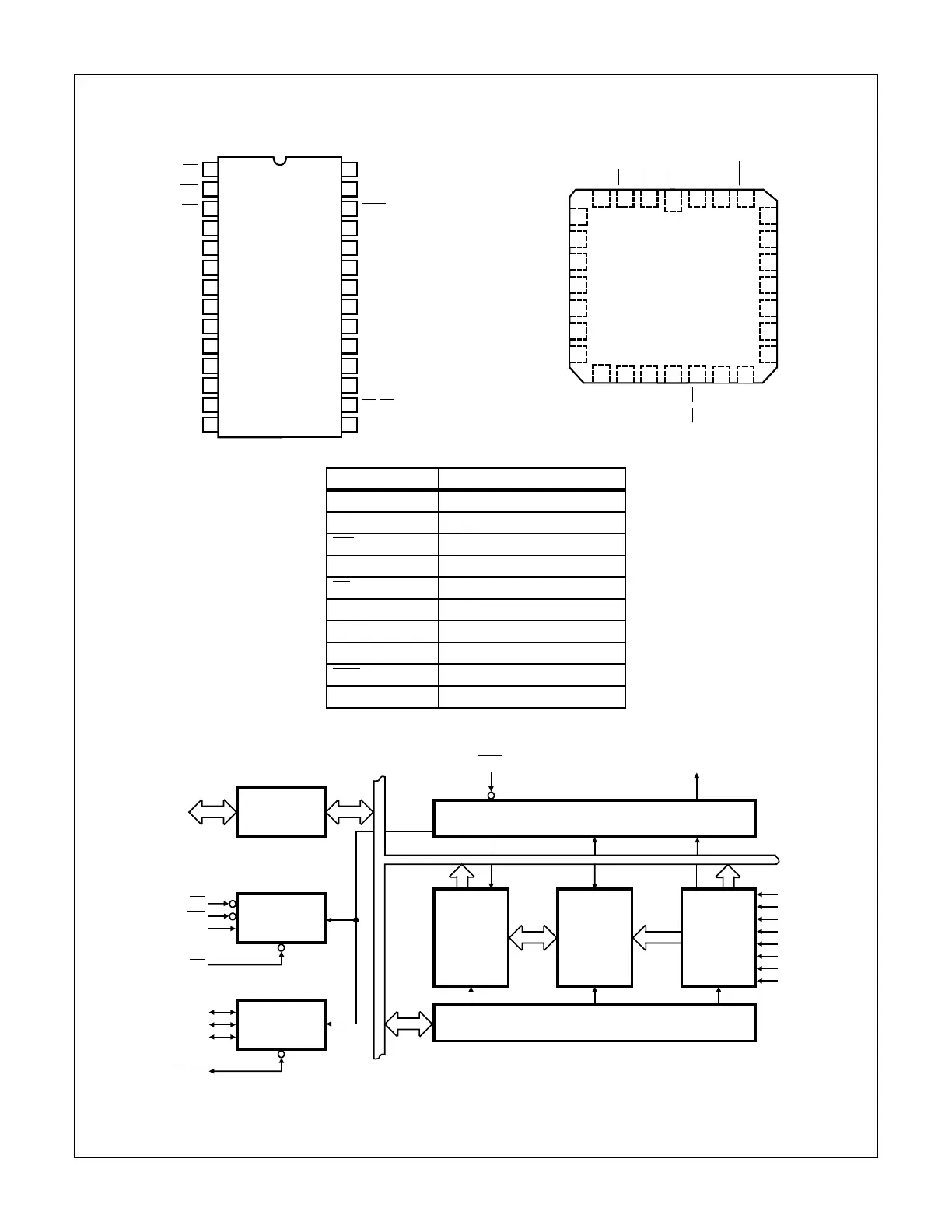

Pinouts

82C59A (PDIP, CERDIP, SOIC)

TOP VIEW

82C59A (PLCC, CLCC)

TOP VIEW

PIN DESCRIPTION

D7 - D0 Data Bus (Bidirectional)

RD Read Input

WR Write Input

A0 Command Select Address

CS Chip Select

CAS 2 - CAS 0 Cascade Lines

SP/EN Slave Program Input Enable

INT Interrupt Output

INTA Interrupt Acknowledge Input

IR0 - IR7 Interrupt Request Inputs

CS

WR

RD

D7

D6

D5

D4

D3

D2

D1

D0

CAS 0

CAS 1

GND

V

CC

INTA

IR7

IR6

IR5

IR3

IR1

IR0

INT

SP/EN

CAS 2

A0

IR4

IR2

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

23

24

25

22

21

20

19

11

3 2

1

4

14 15 16 17 18

12

13

28 27 26

10

5

6

7

8

9

D7

V

CC

A0

RD

WR

CS

INTA

D6

D5

D4

D3

D2

D1

D0

IR7

IR6

IR5

IR4

IR3

IR2

IR1

CAS 0

IR0

CAS 1

GND

CAS 2

SP/ EN

INT

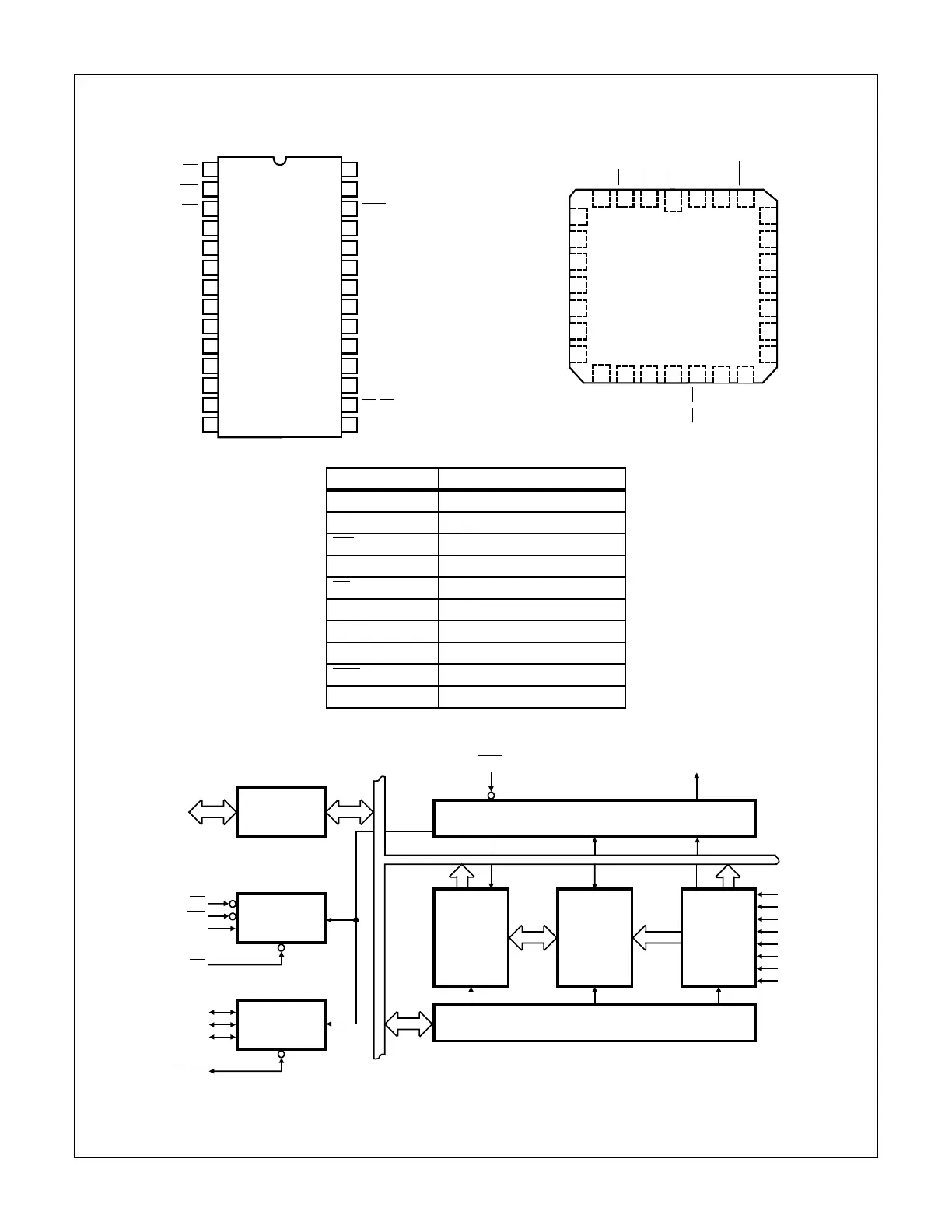

PRIORITY

RESOLVER

IR0

IR1

IR2

IR3

IR4

IR5

IR6

IR7

INTERRUPT

REQUEST

REG

(IRR)

INTERRUPT MASK REG

(IMR)

CONTROL LOGIC

INTERNAL BUS

INT

DATA

BUS

BUFFER

CASCADE

BUFFER

COMPARATOR

CAS 0

CAS 1

CAS 2

READ/

WRITE

LOGIC

SP/EN

WR

RD

INTA

IN -

SERVICE

REG

(ISR)

CS

D

7

-D

0

A

0

FIGURE 1.

82C59A

Loading...

Loading...