4-8

D

7

A

0

D

6

D

5

D

4

D

3

D

2

D

1

D

0

0

A

7

A

6

A

5

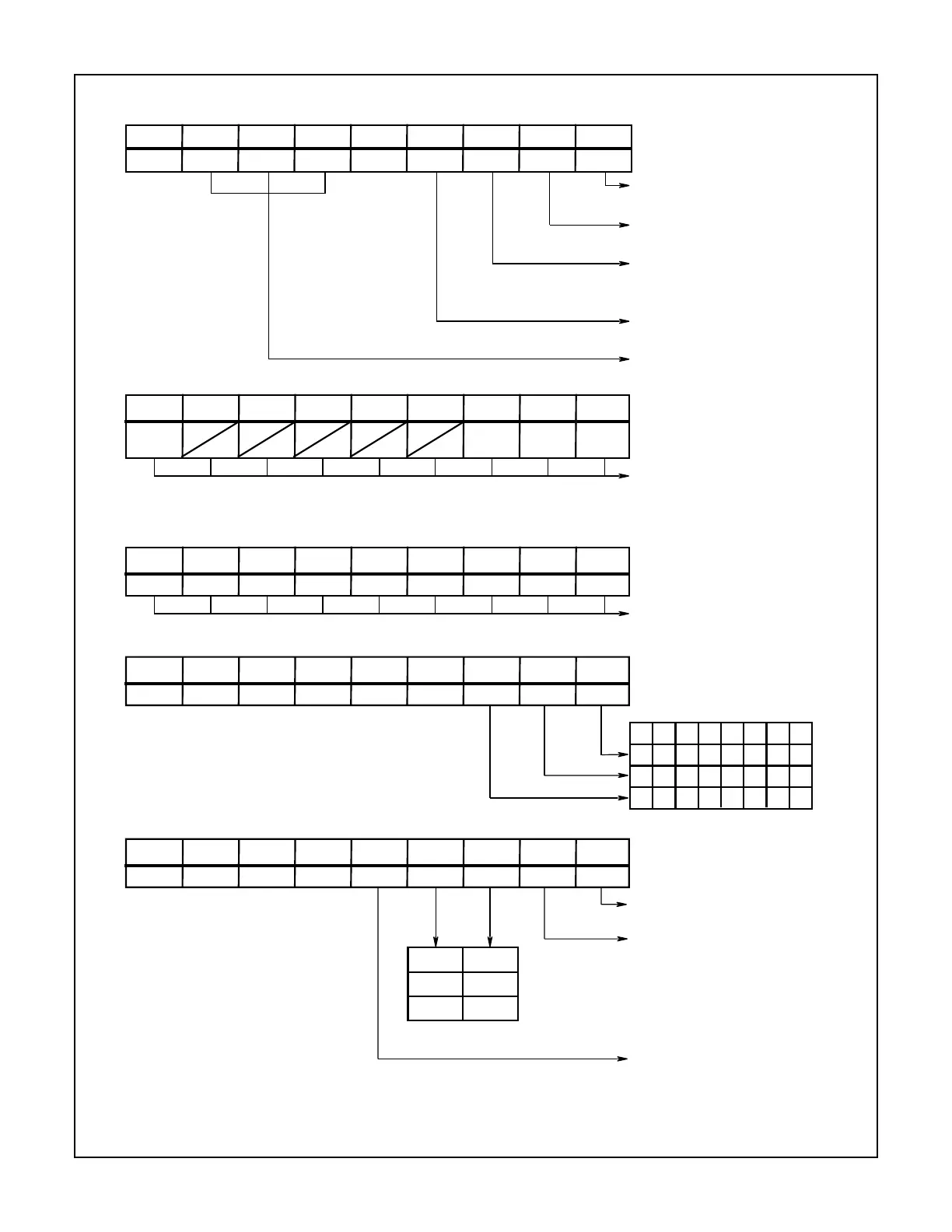

LTIM1 ADI SNGL IC4

ICW1

1 = ICW4 needed

0 = No ICW4 needed

1 = Single

0 = Cascade Mode

CALL address interval

1 = Interval of 4

0 = Interval of 8

1 = Level triggered mode

0 = Edge triggered mode

A

7

- A

5

of Interrupt vector address

(MCS-80/85 mode only)

D

7

A

0

D

6

D

5

D

4

D

3

D

2

D

1

D

0

1

A

15

A

14

A

13

A

11

A

10

A

9

A

8

A

12

T

7

T

6

T

5

T

4

T

3

ICW2

A

15

- A

8

of interrupt vector address

(MCS80/85 mode)

T

7

- T

3

of interrupt vector address

(8086/8088 mode)

D

7

A

0

D

6

D

5

D

4

D

3

D

2

D

1

D

0

1S

7

S

6

S

5

S

3

S

2

S

1

S

0

S

4

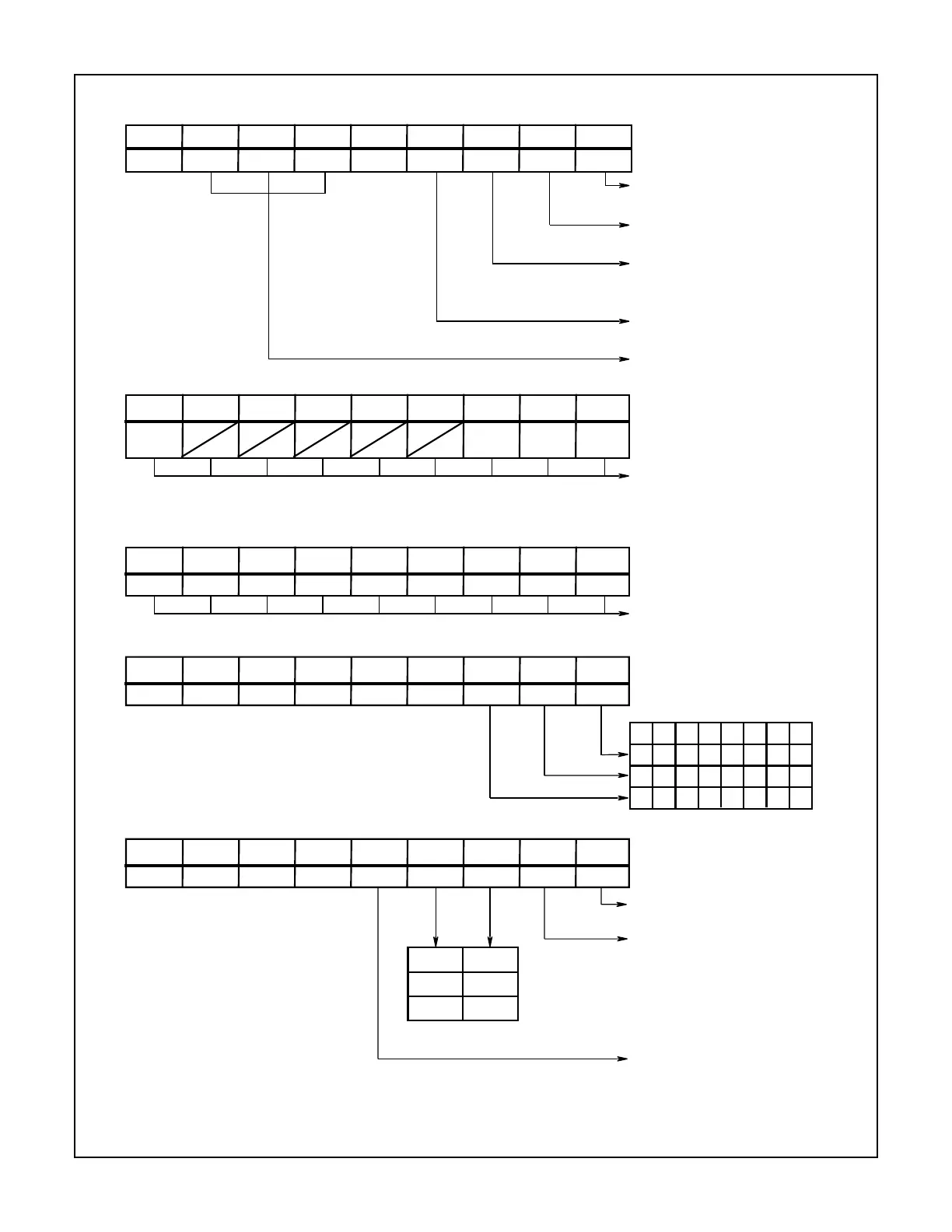

ICW3 (MASTER DEVICE)

1 = IR input has a slave

0 = IR input does not have a slave

D

7

A

0

D

6

D

5

D

4

D

3

D

2

D

1

D

0

1000 0ID

2

ID

1

ID

0

0

ICW3 (SLAVE DEVICE)

SLAVE ID (NOTE)

01 5234 67

01 1010 01

00 0110 11

00 1001 11

D

7

A

0

D

6

D

5

D

4

D

3

D

2

D

1

D

0

1 0 0 0 BUF M/S AEOI µPMSFNM

ICW4

1 = 8086/8088 mode

0 = MCS-80/85 mode

1 = Auto EOI

0 = Normal EOI

0

1

11

0

X - Non buffered mode

- Buffered mode slave

- Buffered mode master

1 = Special fully nested moded

0 = Not special fully nested mode

FIGURE 7. 82C59A INITIALIZATION COMMAND WORD FORMAT

NOTE: Slave ID is equal to the corresponding master IR input.

82C59A

Loading...

Loading...