80C187

and exception. When loading a signalling NaN,

FLD

single/double precision

signals an invalid-

operand exception.

16. The 80C187 only generates quiet NaNs (as on

the 8087); however, the 80C187 distinguishes

between quiet NaNs and signalling NaNs. Sig-

nalling NaNs trigger exceptions when they are

used as operands; quiet NaNs do not (except for

FCOM, FIST, and FBSTP which also raise IE for

quiet NaNs).

17. When stack overflow occurs during FPTAN and

overflow is masked, both ST(0) and ST(1) con-

tain quiet NaNs. The 8087 leaves the original

operand in ST(1) intact.

18. When the scaling factor is

g

%

, the FSCALE

(ST(0), ST(1) instruction behaves as follows

(ST(0) and ST(1) contain the scaled and scaling

operands respectively):

#

FSCALE (0,

%

) generates the invalid opera-

tion exception.

#

FSCALE (finite,

b%

) generates zero with the

same sign as the scaled operand.

#

FSCALE (finite,

a %

) generates

%

with the

same sign as the scaled operand.

The 8087 returns zero in the first case and rais-

es the invalid-operation exception in the other

cases.

19. The 80C187 returns signed infinity/zero as the

unmasked response to massive overflow/under-

flow. The 8087 supports a limited range for the

scaling factor; within this range either massive

overflow/underflow do not occur or undefined

results are produced.

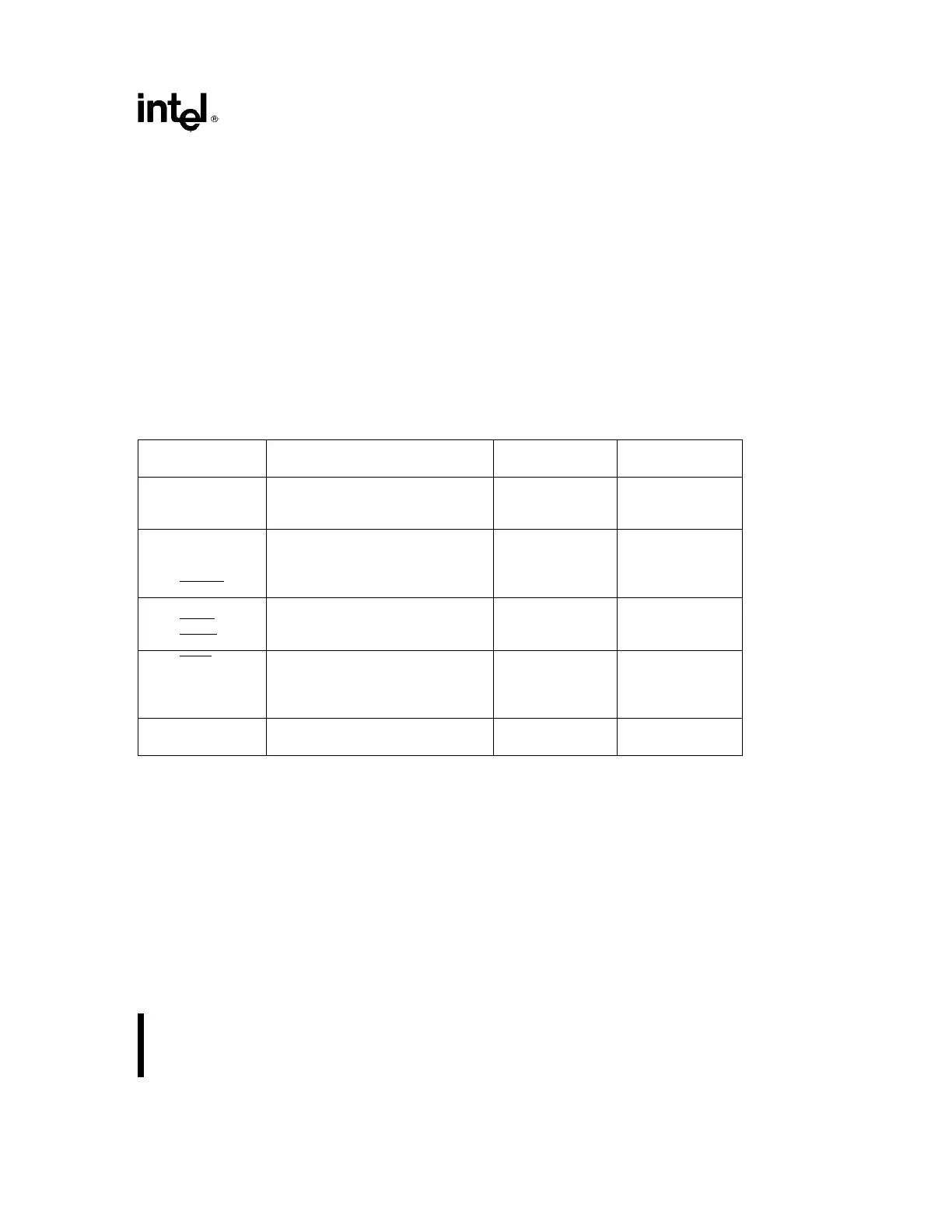

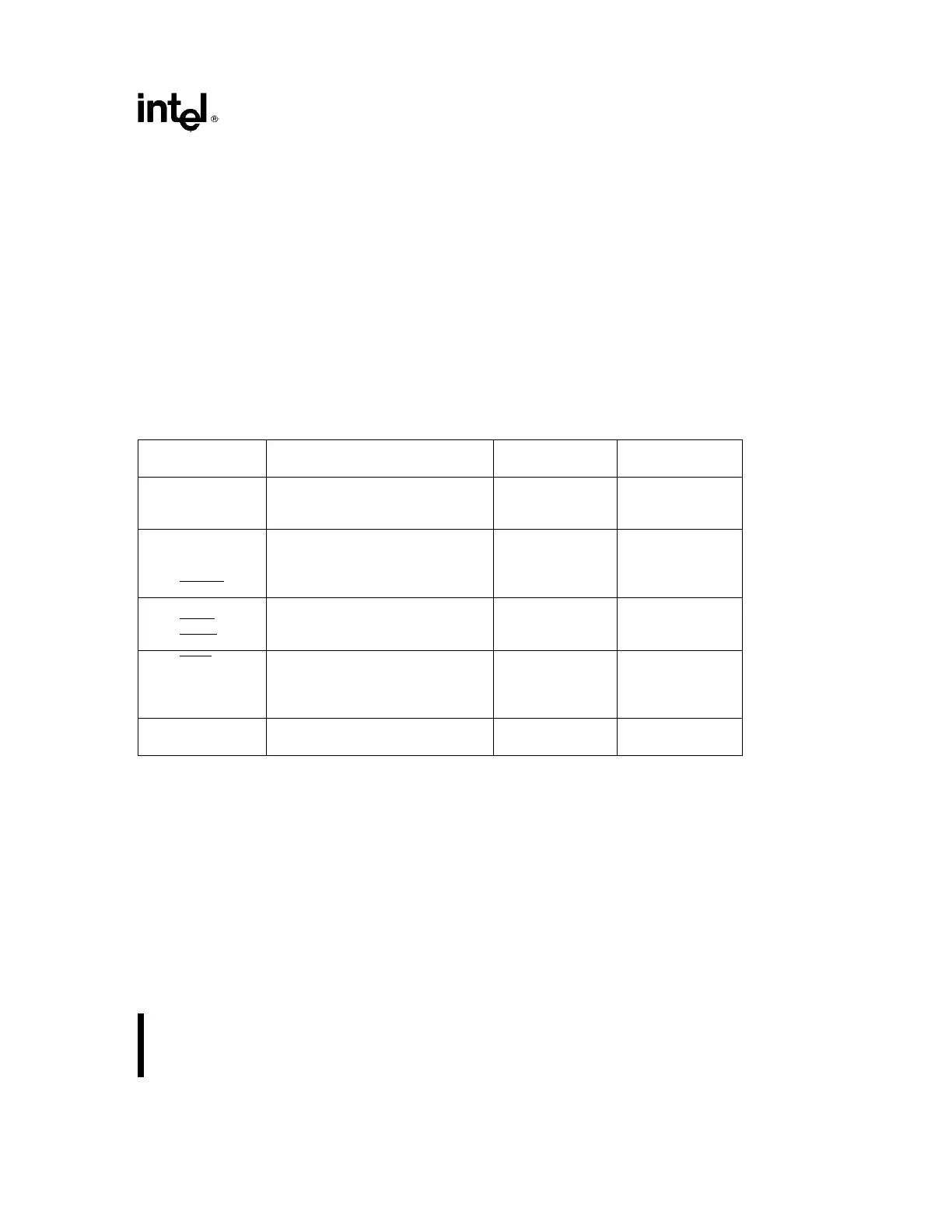

Table 7. Pin Summary

Pin

Function

Active Input/

Name State Output

CLK CLocK I

CKM ClocKing Mode I

RESET System reset High I

PEREQ Processor Extension High O

REQuest

BUSY Busy status High O

ERROR Error status Low O

D

15

–D

0

Data pins High I/O

NPRD

Numeric Processor ReaD Low I

NPWR

Numeric Processor WRite Low I

NPS1 NPX select

Ý

1 Low I

NPS2 NPX select

Ý

2 High I

CMD0 CoMmanD 0 High I

CMD1 CoMmanD 1 High I

V

CC

System power I

V

SS

System ground I

13

Loading...

Loading...