CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 105

All rights reserved. CONFIDENTIAL

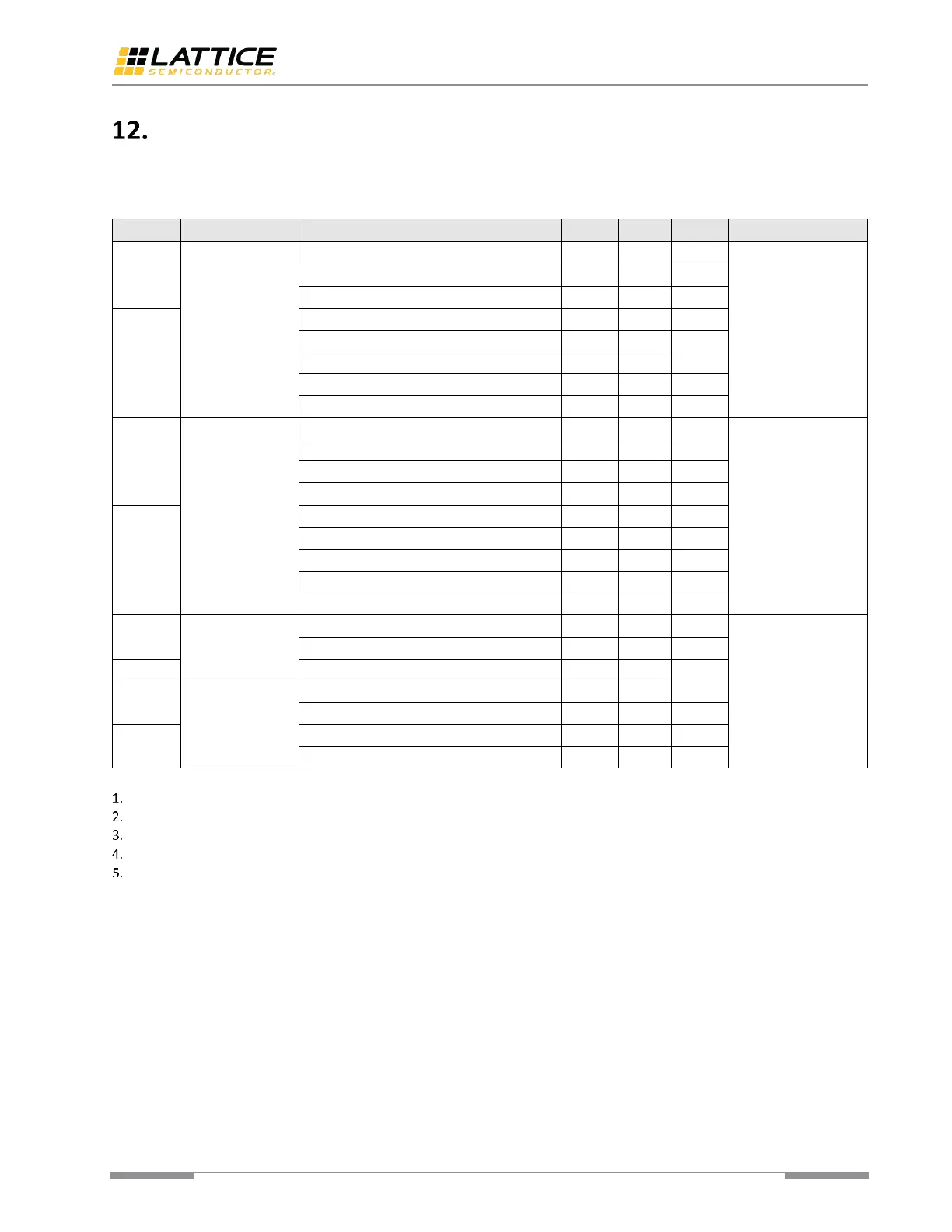

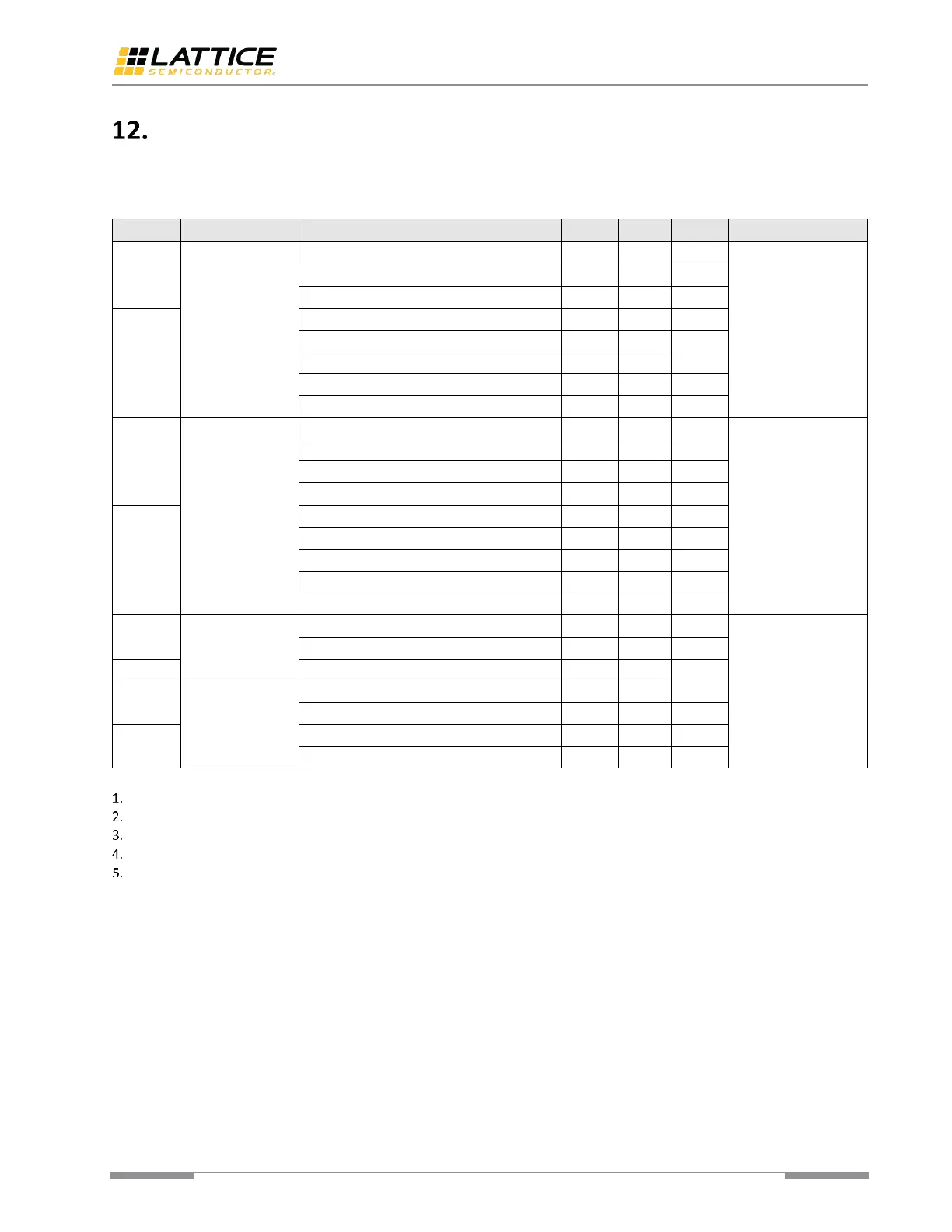

SerDes/PCS Block Latency

Table 12.1 provides transmit and receive latencies respectively in the SerDes, as well as different stages inside the PCS.

The latency is in number of parallel word clocks.

Table 12.1. Transmit/Receive SerDes/PCS Latency

Notes:

Enabled in multi-lane mode. Otherwise, disabled.

The actual value should be added with the max_skew between two different lanes.

The actual value should be added with one EPCS clock cycle.

The actual value should be added with three ECPS clock cycles.

The actual value should be added with one EPCS clock cycle.

Loading...

Loading...