CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 37

All rights reserved. CONFIDENTIAL

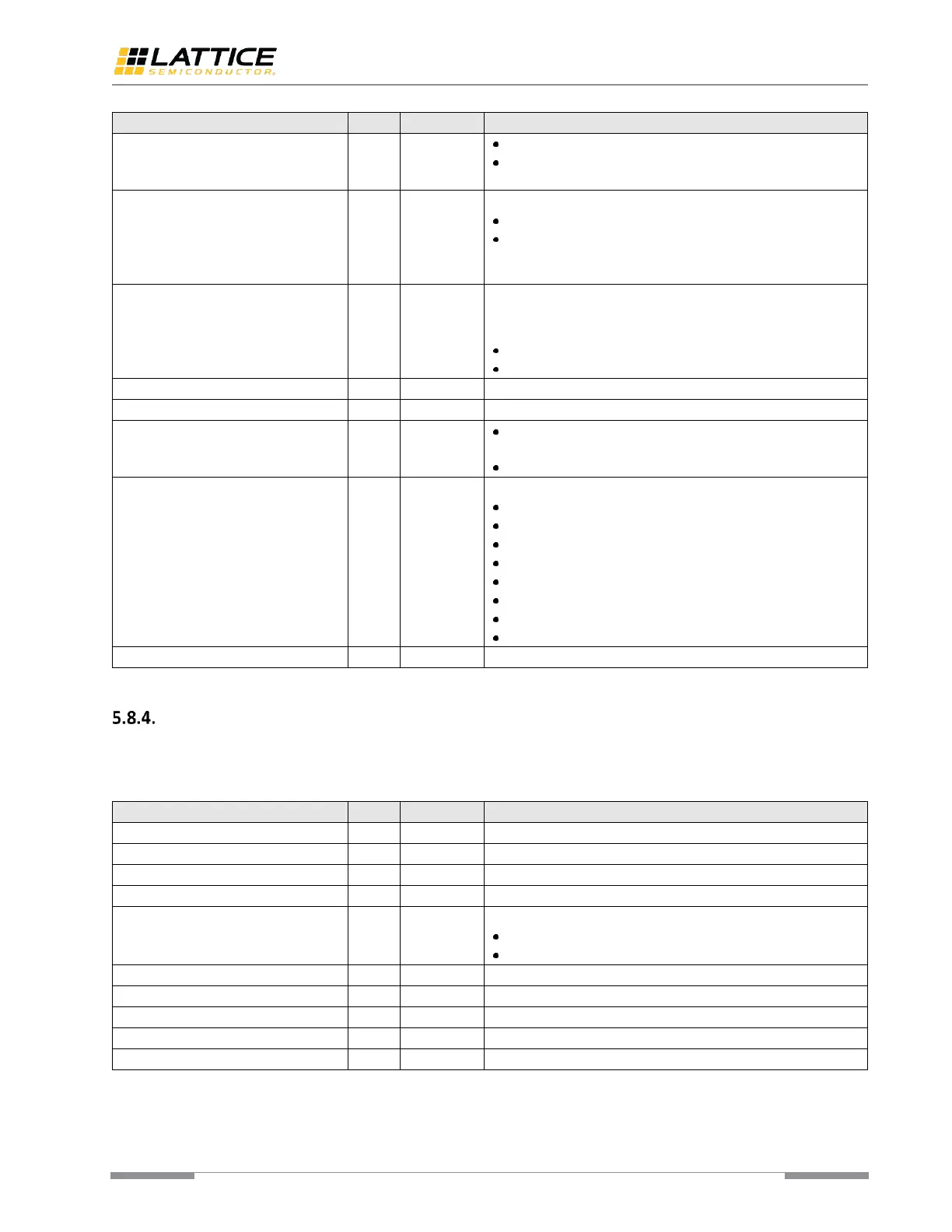

1’b1 – Data is valid.

1’b0 – Data is invalid.

De-asserted only to compensate for 128b130b encoding.

PIPE Rx start block.

1’b1 – Start of the block.

1’b0 – Any occurrence other than the start of the block.

All blocks received are 128-bit, except SKP OS, size of which is a

variable.

PIPE Rx sync header.

When pipe_rx_start_block_LL_o == 1’b1, it indicates the block

type:

2’b01 – Ordered set.

2’b10 – Data.

PIPE Rx data K indicator for 8b10b.

1’b1 – PHY is locked to Rx data stream and data is valid, use

pipe_rx_data_LL_o.

1’b0 – PHY is not locked, ignore pipe_rx_data_LL_o.

PIPE Rx status.

3’b000 – Reserved.

3’b001 – SKP added.

3’b010 – SKP deleted.

3’b011 – Receiver detected.

3’b100 – Encoding error.

3’b111 – Disparity error.

3’b101 – Overflow error.

3’b110 – Underflow error.

PIPE clock connected to the hard PCIe Link Layer Quad.

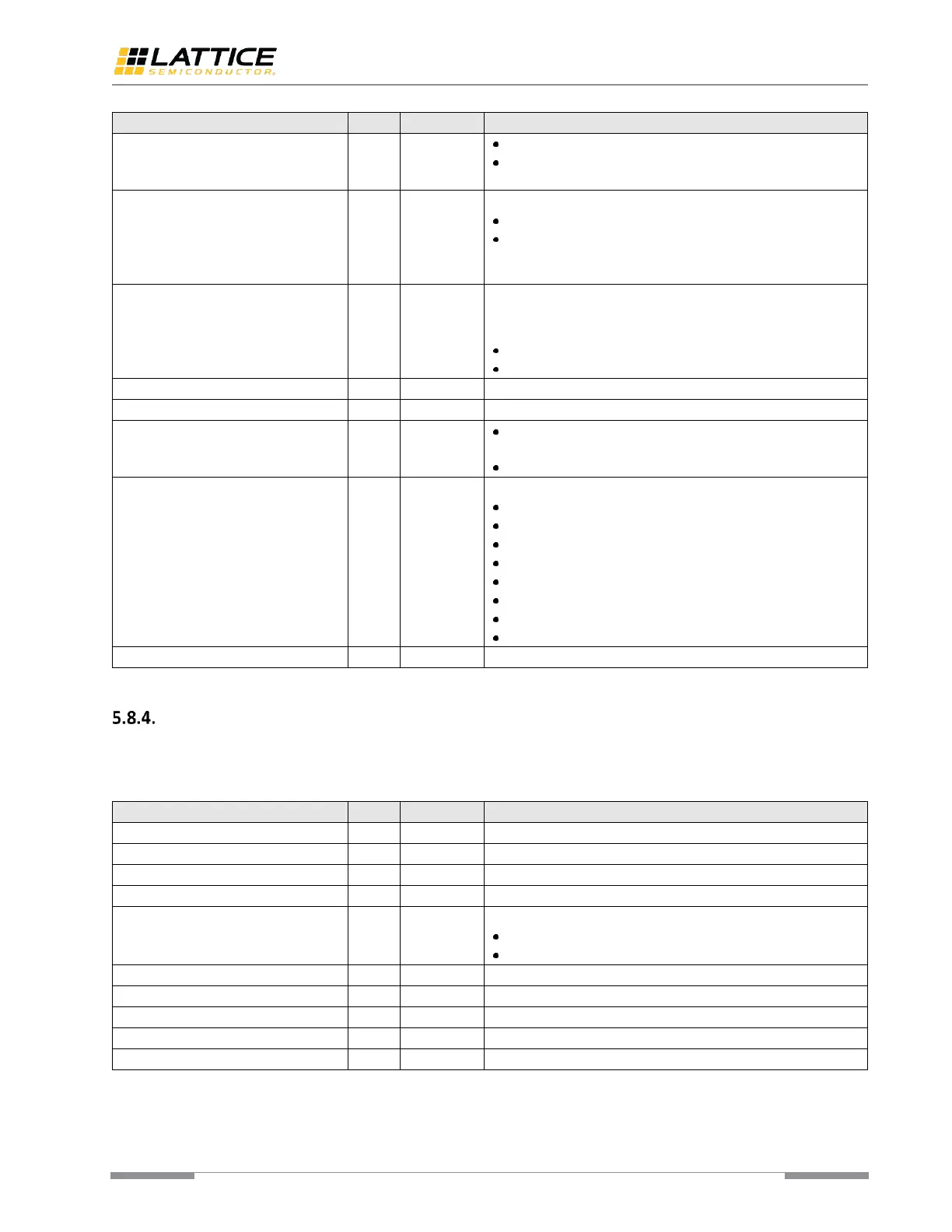

LMMI Interface

LMMI is simple memory mapped interface proposed by Lattice, and is mainly used for register access. Table 5.10 shows

the detailed LMMI interface descriptions. All these signals are per lane, and NL means the number of lanes.

Table 5.10. LMMI Interface

Address/Offset, the highest bit is used to select register space.

1’b1 – MPCS register space.

1’b0 – PMA register space.

Loading...

Loading...