CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 139

All rights reserved. CONFIDENTIAL

is not ignored during alignment pattern matching.

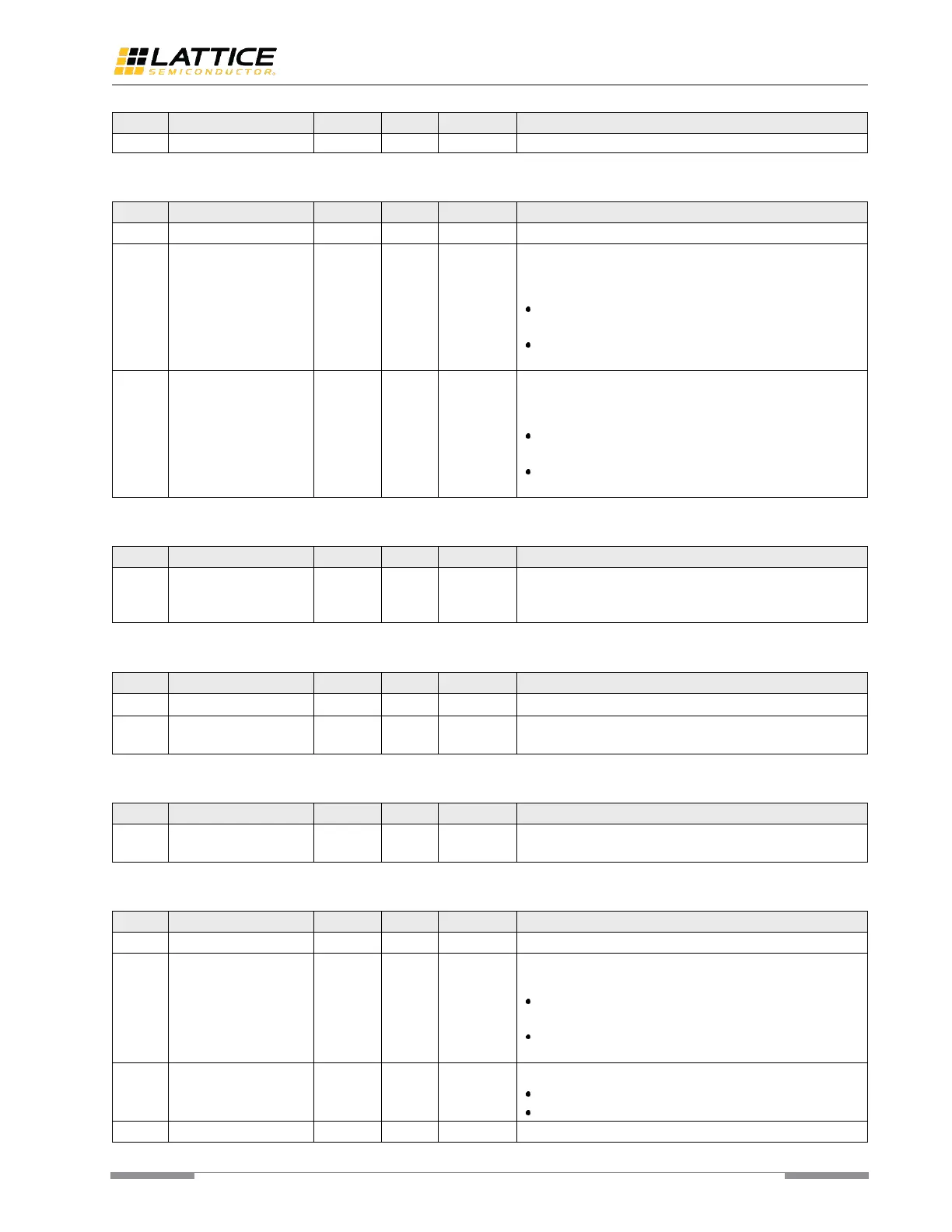

Table A. 46. Word Alignment Pattern Mask Code MSB [reg39]

Word Align Mask Mode. Specifies the 20-bit word

alignment pattern. In 10-bit width mode, only bits 9 to 0

are applied.

1’b1 – the corresponding bit of word alignment pattern

is ignored during alignment pattern matching.

1’b0 – the corresponding bit of word alignment pattern

is not ignored during alignment pattern matching.

Word Align Mask Mode. Specifies the 20-bit word

alignment pattern. In 10-bit width mode, only bits 9 to 0

are applied.

1’b1 – The corresponding bit of word alignment pattern

is ignored during alignment pattern matching.

1’b0 – The corresponding bit of word alignment pattern

is not ignored during alignment pattern matching.

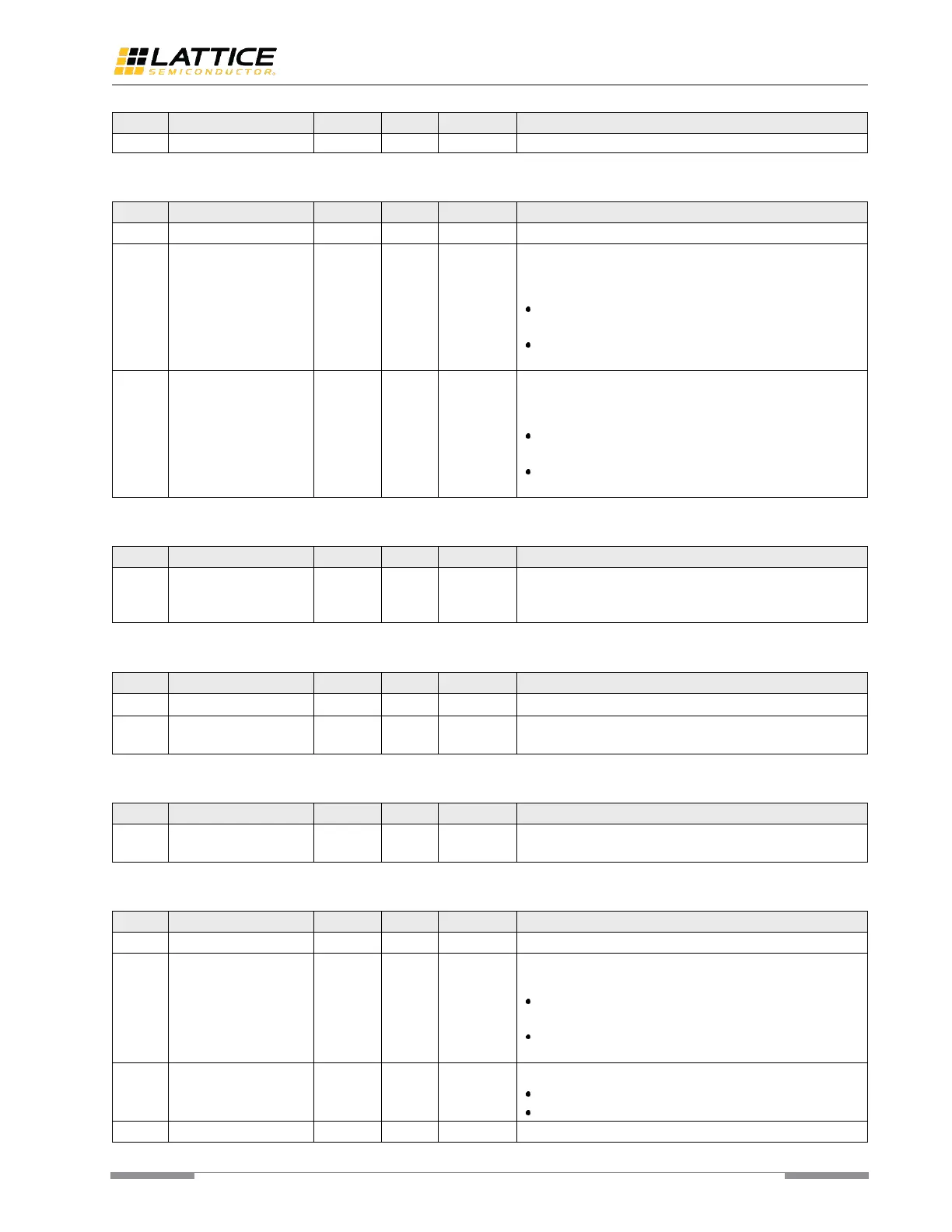

Table A. 47. Sync_Det FSM Configuration 0 [reg3a]

Specifies the number of valid synchronization code groups

or ordered sets that “sync_det” FSM must receive to

achieve synchronization state.

Table A. 48. Sync_Det FSM Configuration 1 [reg3b]

Specifies the number of bad code groups received by

“sync_det” FSM to conclude the loss of synchronization.

Table A. 49. Sync_Det FSM Configuration 2 [reg3c]

Specifies the continuous good code groups received by

“sync_det” FSM to reduce the error count by one.

Table A. 50. Sync_Det FSM Configuration 3 [reg3d]

Secondary Sync Detect Pattern. Specifies the secondary

detect pattern is enabled or disabled.

1’b1 – disable secondary sync_det pattern and do not

use it for matching.

1’b0 – use the secondary sync_det pattern for

matching.

Sync Detect Pattern. Specifies the pattern code.

1’b1 – the sync_det pattern is 10b code.

1’b0 – the sync_det pattern is 8b code.

Pattern Alignment check. Specifies the pattern alignment

Loading...

Loading...