CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

122 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

Appendix A. Configuration Registers

A.1. PMA Registers

A.1.1. Register Address

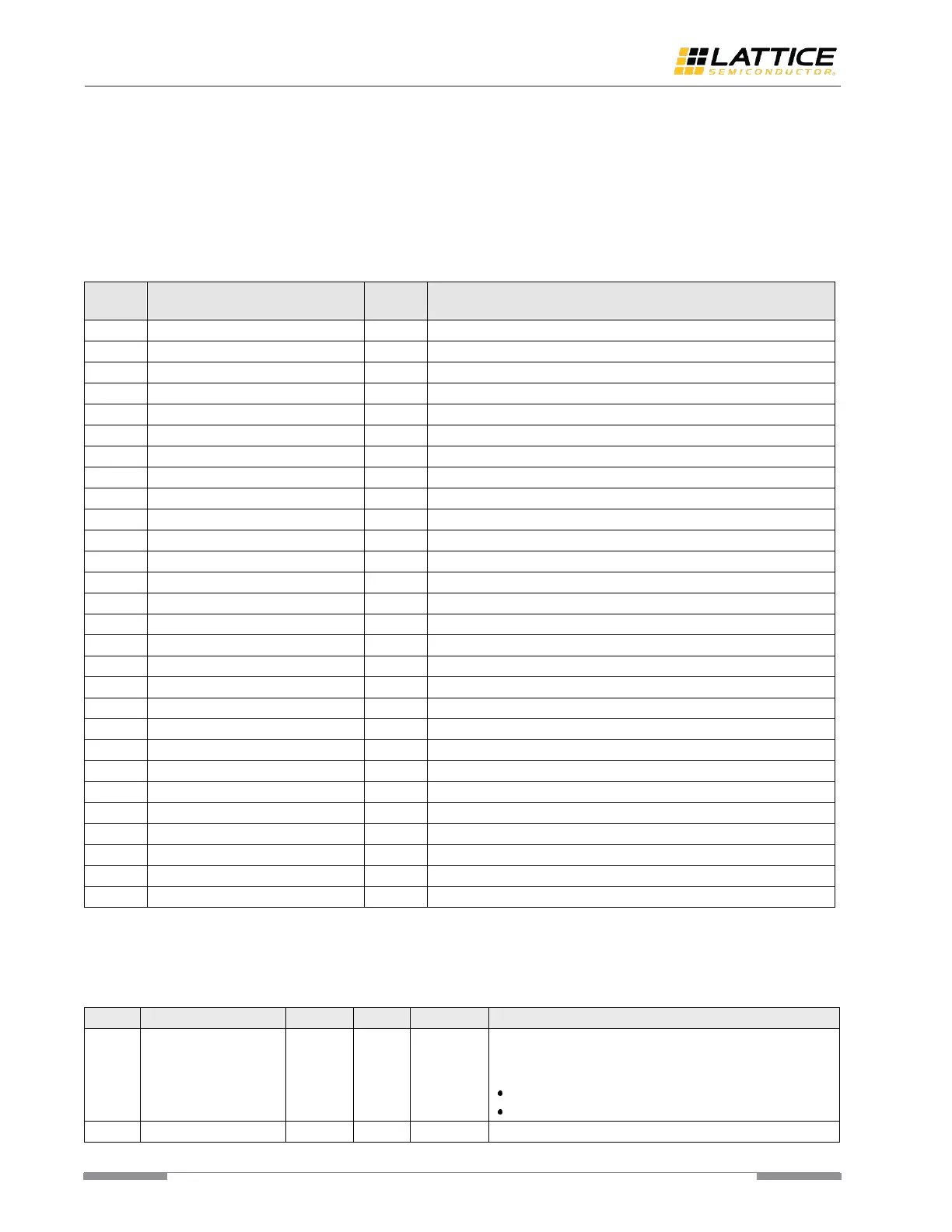

Table A. 1. Register Address

Clock count for error counter decrement.

Error counter threshold – Rx idle detect maximum latency.

Tx PLL F settings and PCLK ratio.

Rx PLL F settings and PCLK ratio.

CDR PLL frequency comparator maximum difference.

CDR PLL frequency comparator counter.

PRBS error counter register.

PHY reset override register.

PHY power override register.

Transmit PLL Current Charge Pump.

Receive PLL Current Charge Pump.

Update settings command register.

A.1.2. Register Description

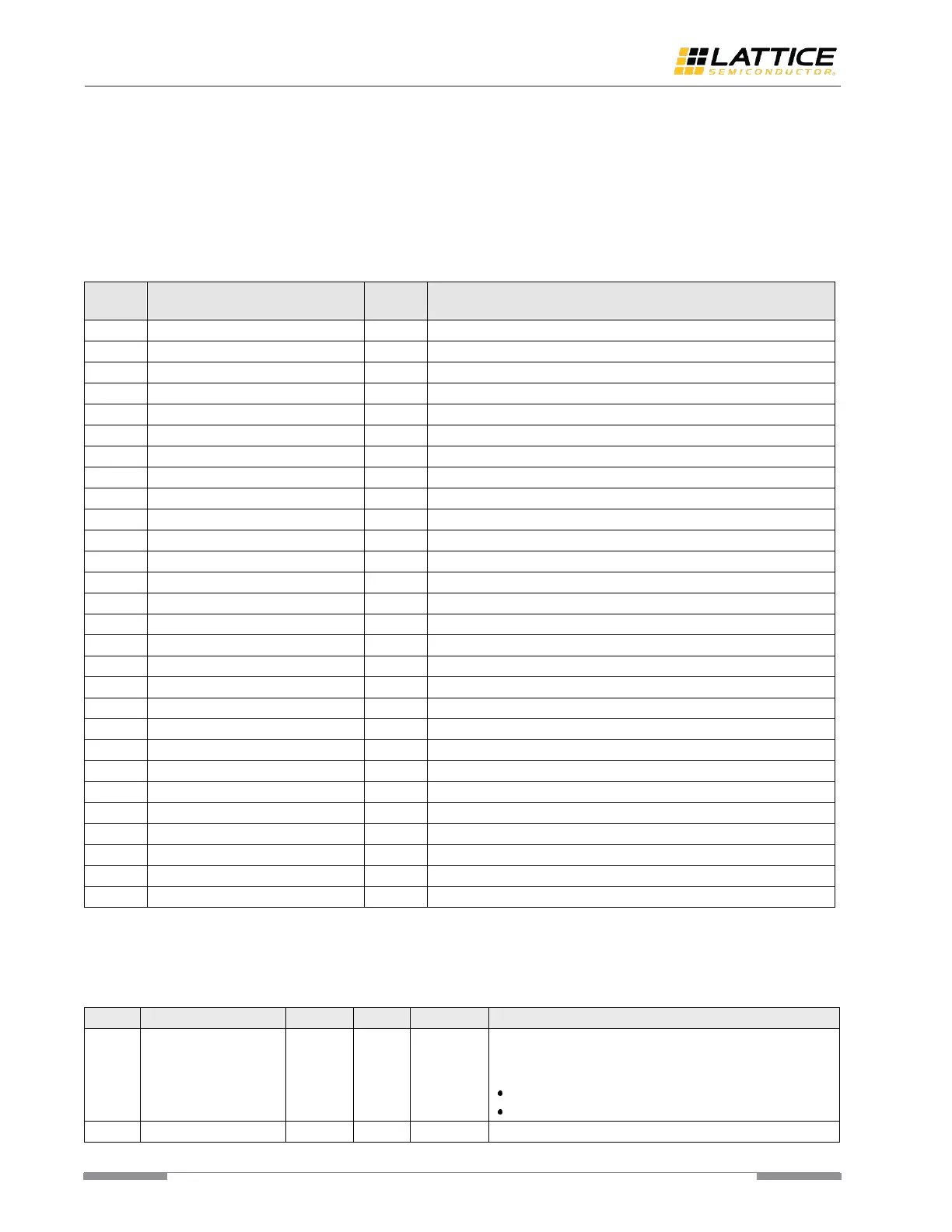

Table A. 2. Control Register 0 [reg00]

Defines whether or not Electrical Idle 1 pattern is

automatically shifted in SerDes macro after loading the

drive pattern.

1’b1 – automatically shifted.

1’b0 – not automatically shifted.

Force the result of PCIe receiver detect operation to be

Loading...

Loading...