CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

74 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

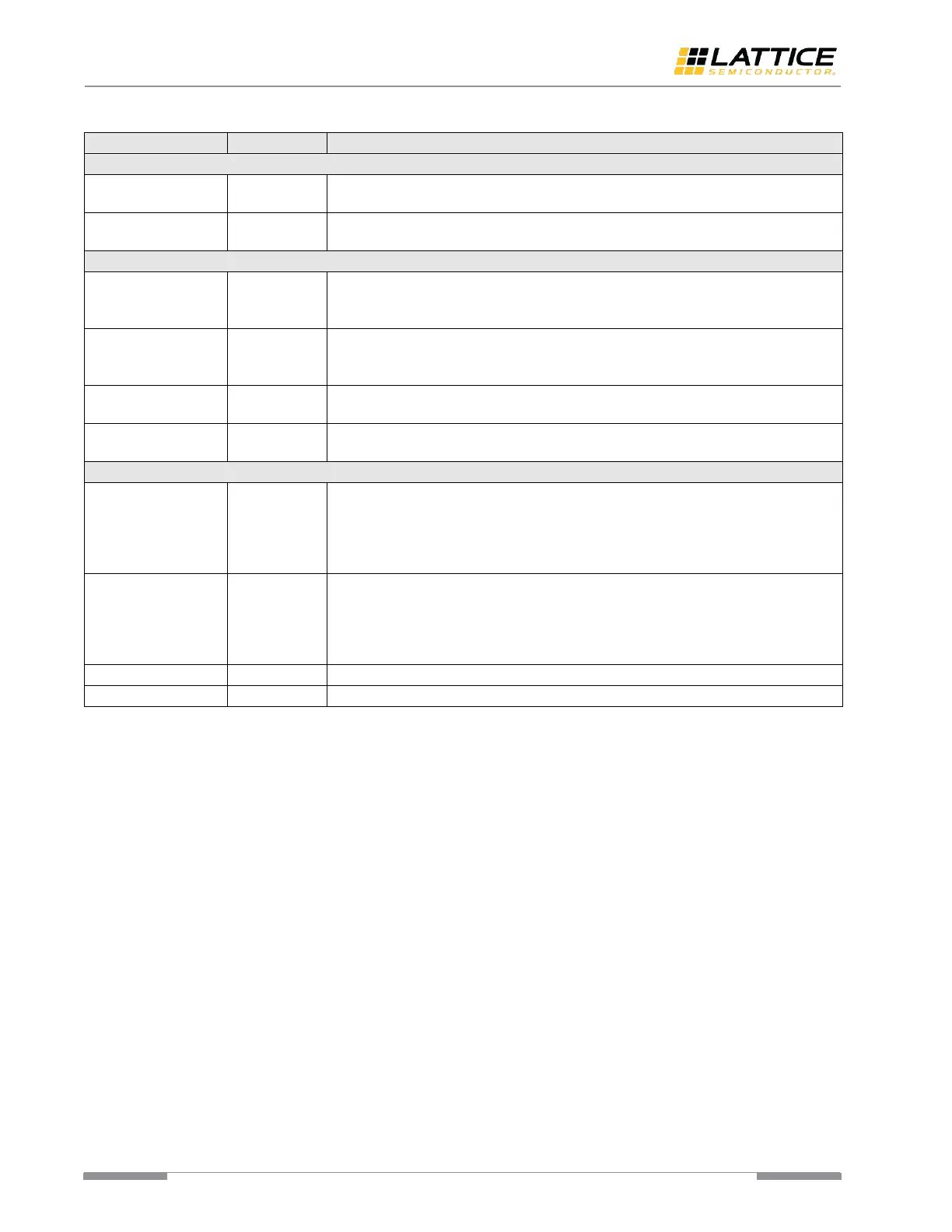

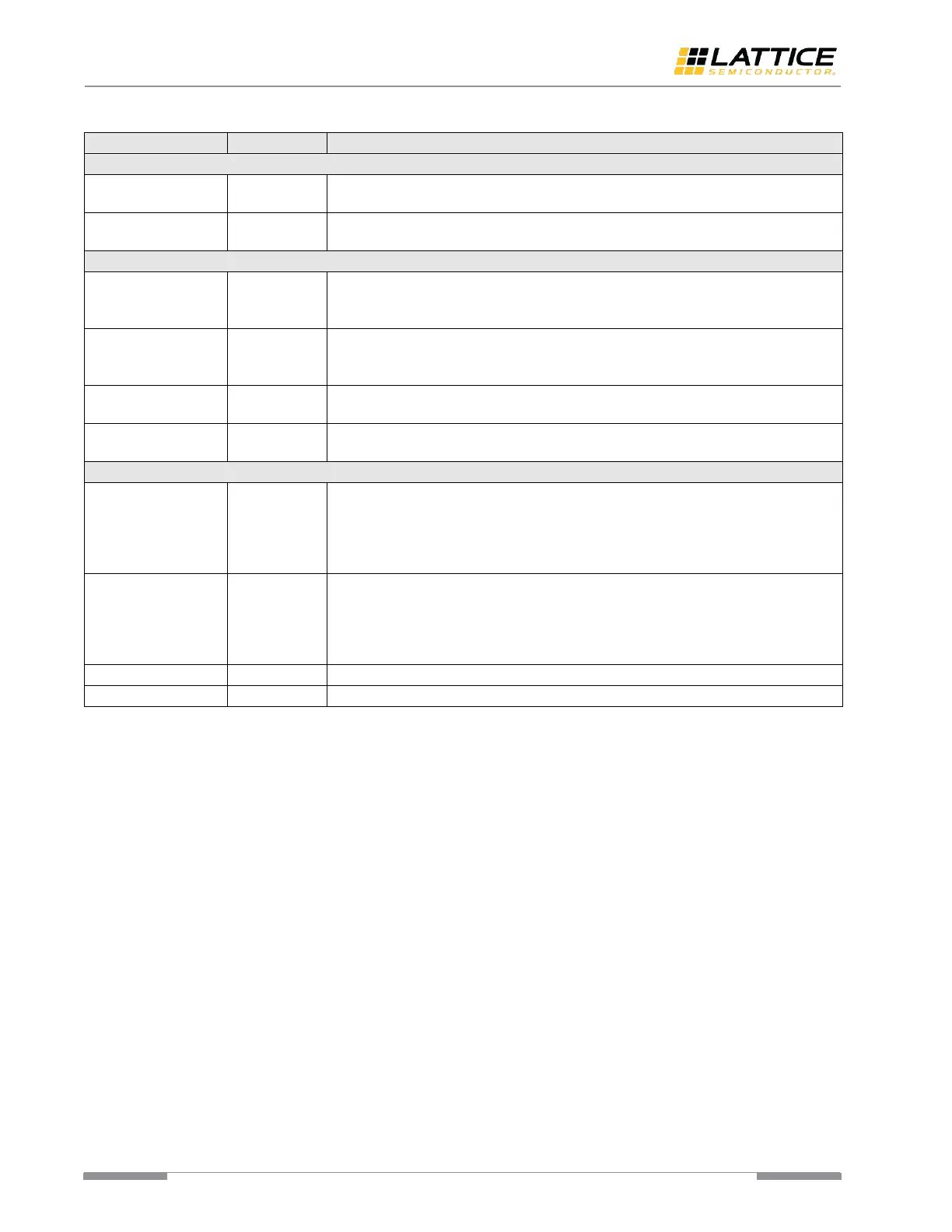

Table 7.2. 64B/66B PCS Channel Clock

PMA Interface (Hardened Connection)

This parallel data clock is generated by PMA Tx macro and used by MPCS to drive Tx

data bus. The source of this clock is Tx PLL.

This parallel data clock is generated by PMA Rx macro and used by MPCS to receive

data from Rx data bus. The source of this clock is the recovered clock from Rx CDR.

This clock is directly connected to FPGA global buffer, and thus can drive FPGA clock

tree. The source of this clock is selected by MPCS, depending on application cases.

This clock can be the divided-by-two version of its source clock.

This clock is directly connected to FPGA global buffer, and thus can drive FPGA clock

tree. The source of this clock is selected by MPCS, depending on application cases

This clock can be the divided-by-two version of its source clock.

This clock is a node of fabric clock tree. The data sent by user logic to MPCS is

synchronous to this clock.

This clock is a node of fabric clock tree. The data received by user logic from MPCS is

synchronous to this clock.

This clock is divided-by-four version of tx_pcs_clk. It is used to drive most part of the

64B/66B PCS Tx path sub-modules.

This clock and tx_pcs_clk are positive edge aligned, with as little skew as possible

between them, so that output data from this clock domain can be sampled by

tx_pcs_clk directly.

This clock is divided-by-four version of rx_pcs_clk. It is used to drive most part of the

64B/66B PCS Rx path sub-modules.

This clock and rx_pcs_clk are positive edge aligned, with as little skew as possible

between them, so that output data from rx_pcs_clk clock domain can be sampled by

rx_pcs_divclk directly.

This clock is divided-by-two version of tx_pcs_clk.

This clock is divided-by-two version of rx_pcs_clk.

Loading...

Loading...