CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 93

All rights reserved. CONFIDENTIAL

SerDes/PCS Debug Capabilities

Loopback Mode

CertusPro-NX SerDes/PCS supports up to seven loopback modes for different test purposes:

PMA Near-End Serial Loopback Mode

PMA Far-End Parallel Loopback Mode

8B/10B PCS Near-End Parallel Loopback Mode

8B/10B PCS Far-End Parallel Loopback Mode

64B/66B PCS Loopback Path A

64B/66B PCS Loopback Path B

64B/66B PCS Loopback Path C

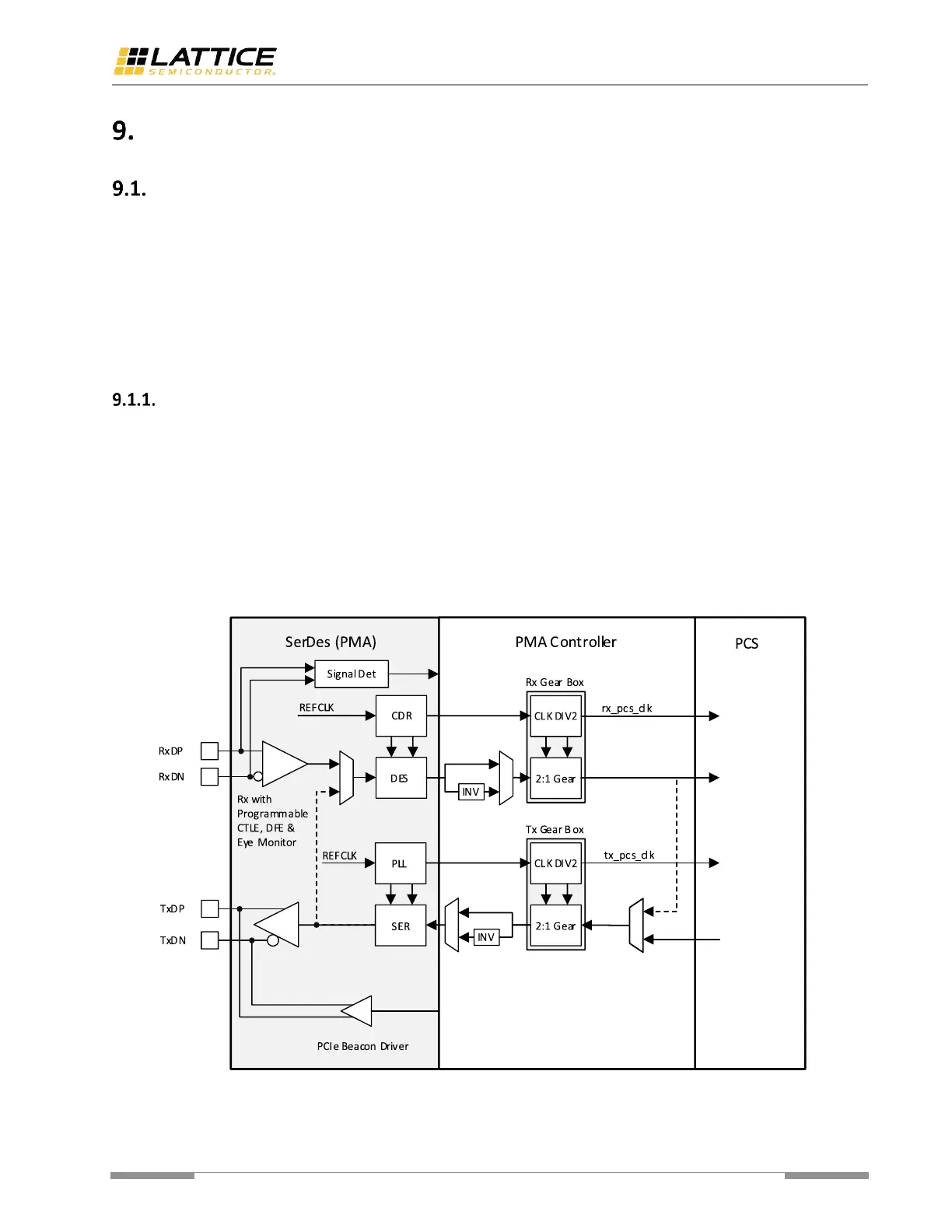

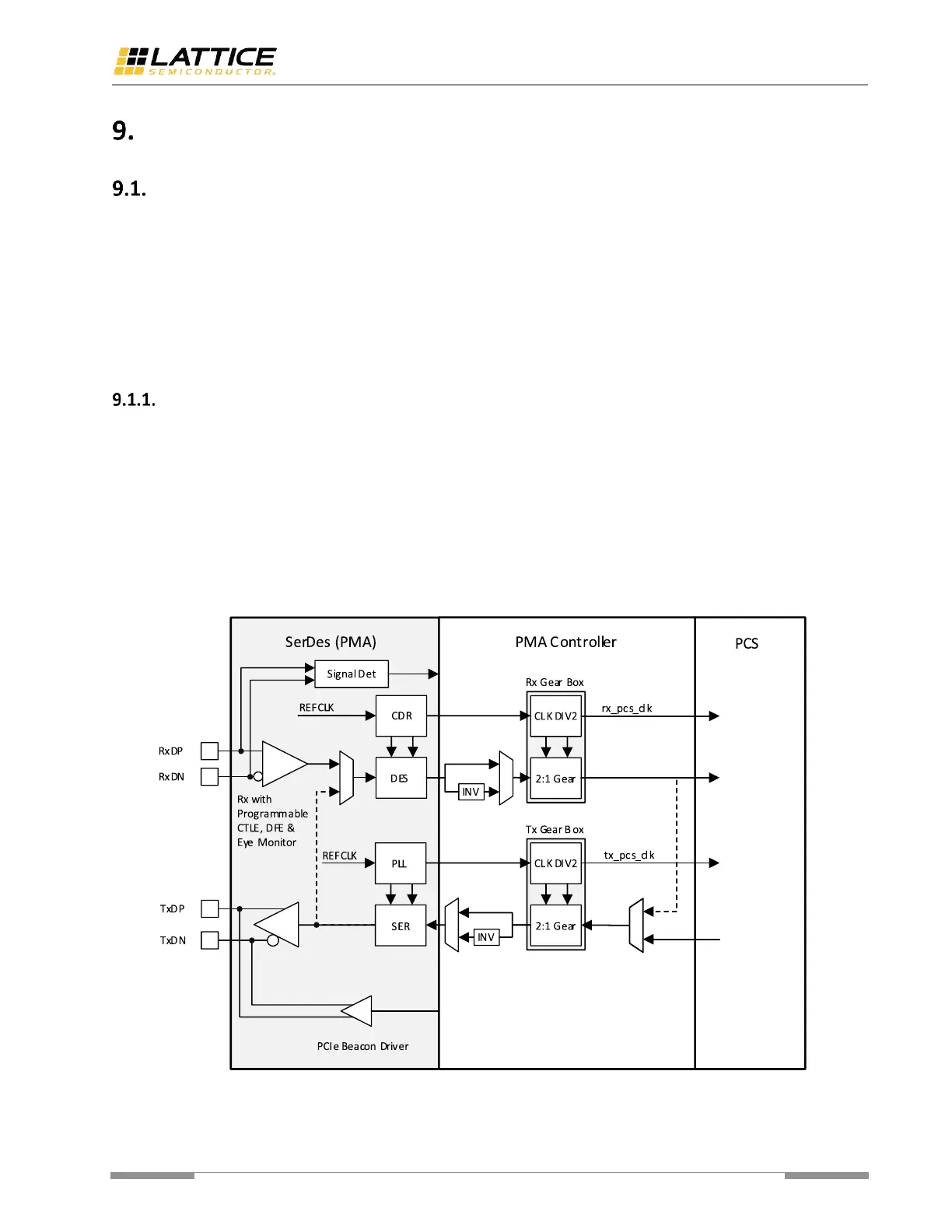

PMA Loopback

Figure 9.1 shows the two loopback modes implemented by PMA and PMA Controller, PMA Near-End Serial Loopback

Mode and PMA Far-End Parallel Loopback Mode.

In the near end serial loopback mode, the serial data from Tx path is fed back to the Rx PMA (CDR and DES). The Rx

PMA extracts clock and data from the bit stream generated by Tx path. This loopback mode can be enabled or disabled

by the bit[1] of PMA register reg100.

In the far end parallel loopback mode, the parallel data received from Rx PMA is transmitted to Tx PMA directly. This

mode requires no clock frequency difference between Rx path and Tx path. Otherwise, user logic must implement bit

skip functionality with the Rx PMA.

Figure 9.1. PMA Loopback Mode

Loading...

Loading...