CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

76 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

This is a common clock shared by channels within Quad.

It is used in multiple-channel application cases. In Tx path, a common clock is used to

align all channels in order to minimize the lane-to-lane skew.

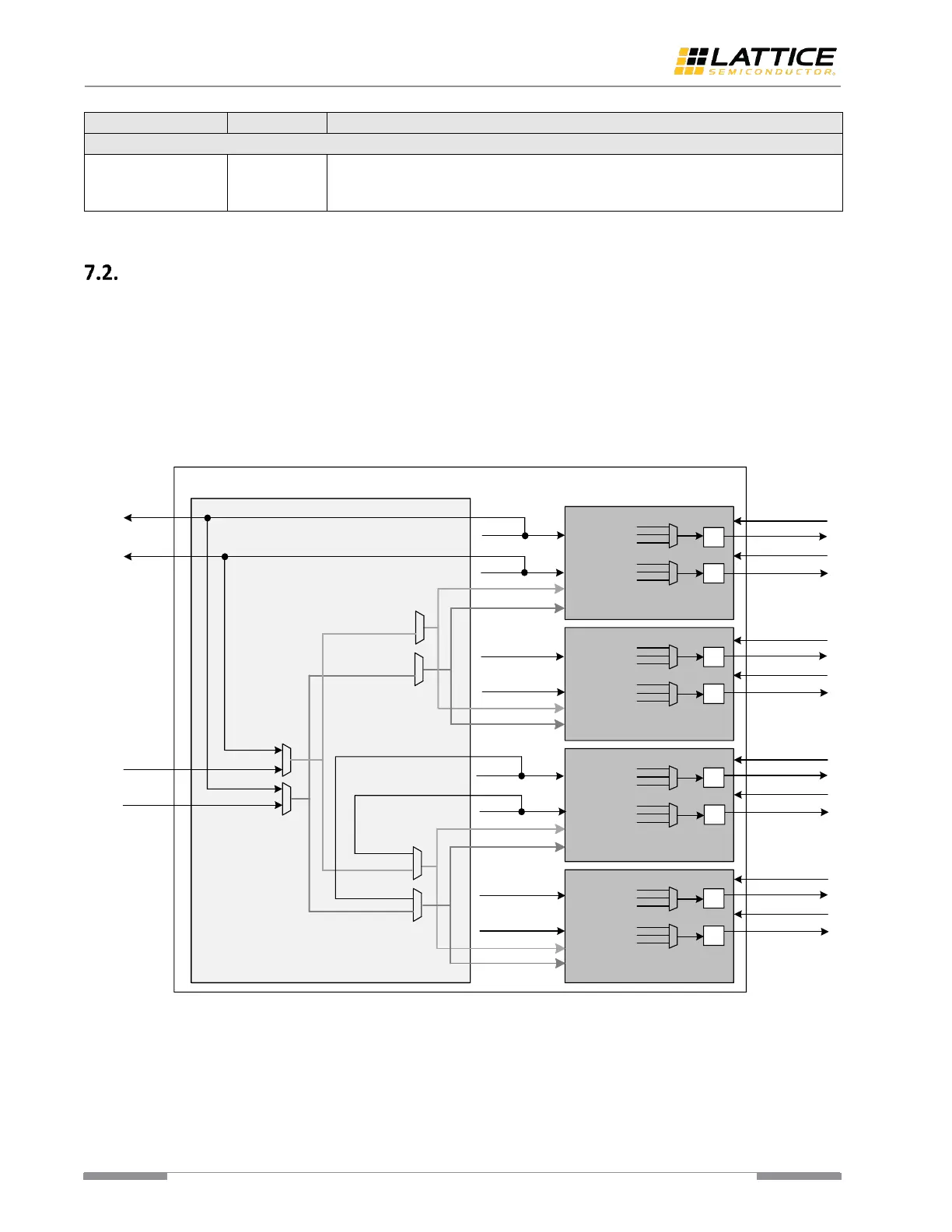

MPCS Quad Clock Detail

This section describes the clock distribution inside one Quad in detail. Figure 7.4 shows MPCS Quad clock distribution

diagram. Table 7.4 is the detailed Quad clock description. The Quad Common module implements the clock

multiplexing and distributing functionalities for multiple-channel applications.

The tx_pcs_clk and rx_pcs_clk from channel 0 are connected to Quad Common module and outside of MPCS Quad. The

tx_pcs_clk[0] and rx_pcs_clk[0] can be connected to all four channels inside the Quad. The tx_pcs_clk and rx_pcs_clk

from channel 2 are connected to Quad Common module, too, but tx_pcs_clk[2] and rx_pcs_clk[2] can be connected to

channel 2 and channel 3 only by Quad Common module. These clock connections bring some limitation on the

implementation for multiple-channel applications. Check the Quad Common section for more details.

Loading...

Loading...