CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 149

All rights reserved. CONFIDENTIAL

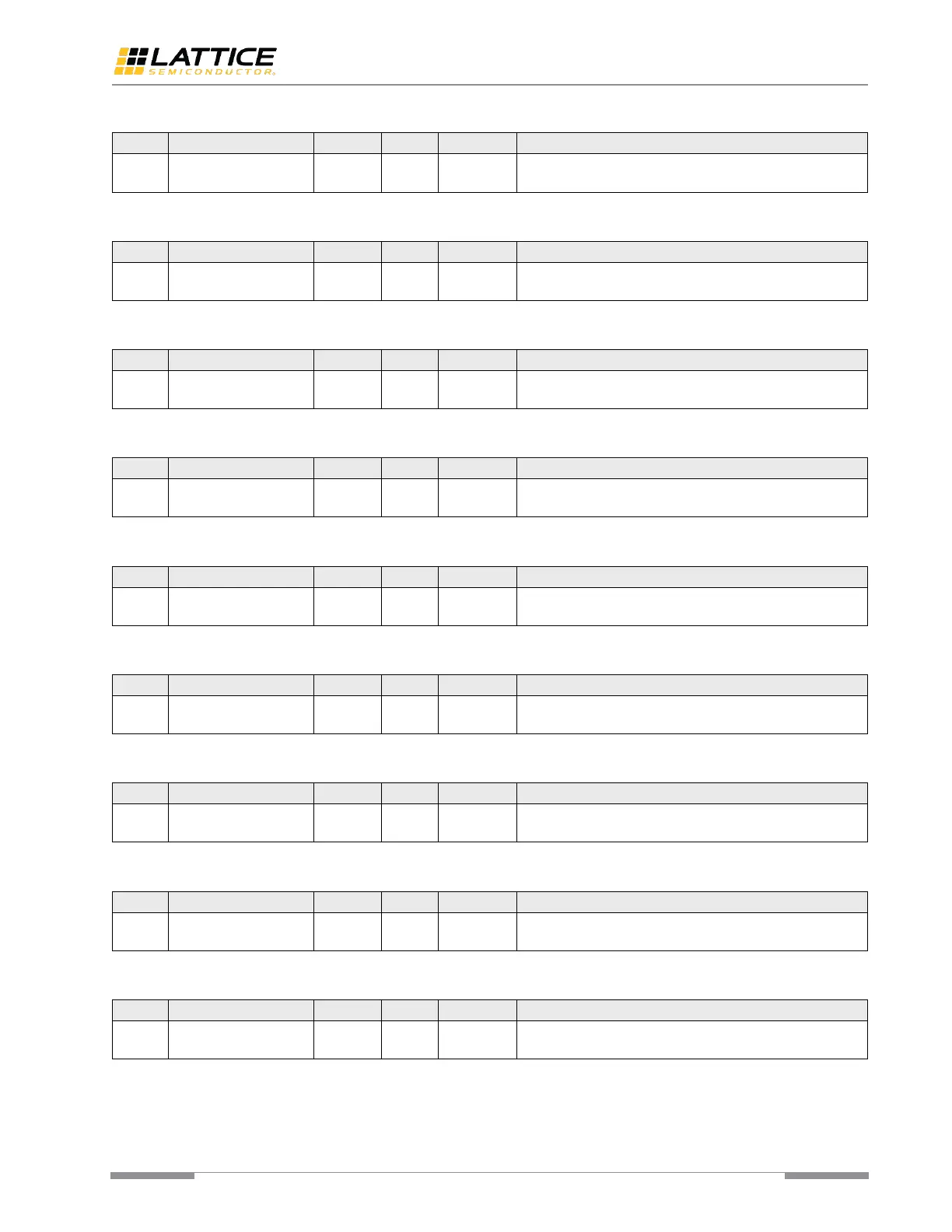

Table A. 111. 10GBASE-R Test Pattern Seed A Byte 7 [reg99]

This register defines byte 7 of 10GBASE-R PCS test pattern

seed A.

Table A. 112. 10GBASE-R Test Pattern Seed B Byte 0 [reg9a]

This register defines byte 0 of 10GBASE-R PCS test pattern

seed B.

Table A. 113. 10GBASE-R Test Pattern Seed B Byte 1 [reg9b]

This register defines byte 1 of 10GBASE-R PCS test pattern

seed B.

Table A. 114. 10GBASE-R Test Pattern Seed B Byte 2 [reg9c]

This register defines byte 2 of 10GBASE-R PCS test pattern

seed B.

Table A. 115. 10GBASE-R Test Pattern Seed B Byte 3 [reg9d]

This register defines byte 3 of 10GBASE-R PCS test pattern

seed B.

Table A. 116. 10GBASE-R Test Pattern Seed B Byte 4 [reg9e]

This register defines byte 4 of 10GBASE-R PCS test pattern

seed B.

Table A. 117. 10GBASE-R Test Pattern Seed B Byte 5 [reg9f]

This register defines byte 5 of 10GBASE-R PCS test pattern

seed B.

Table A. 118. 10GBASE-R Test Pattern Seed B Byte 6 [rega0]

This register defines byte 6 of 10GBASE-R PCS test pattern

seed B.

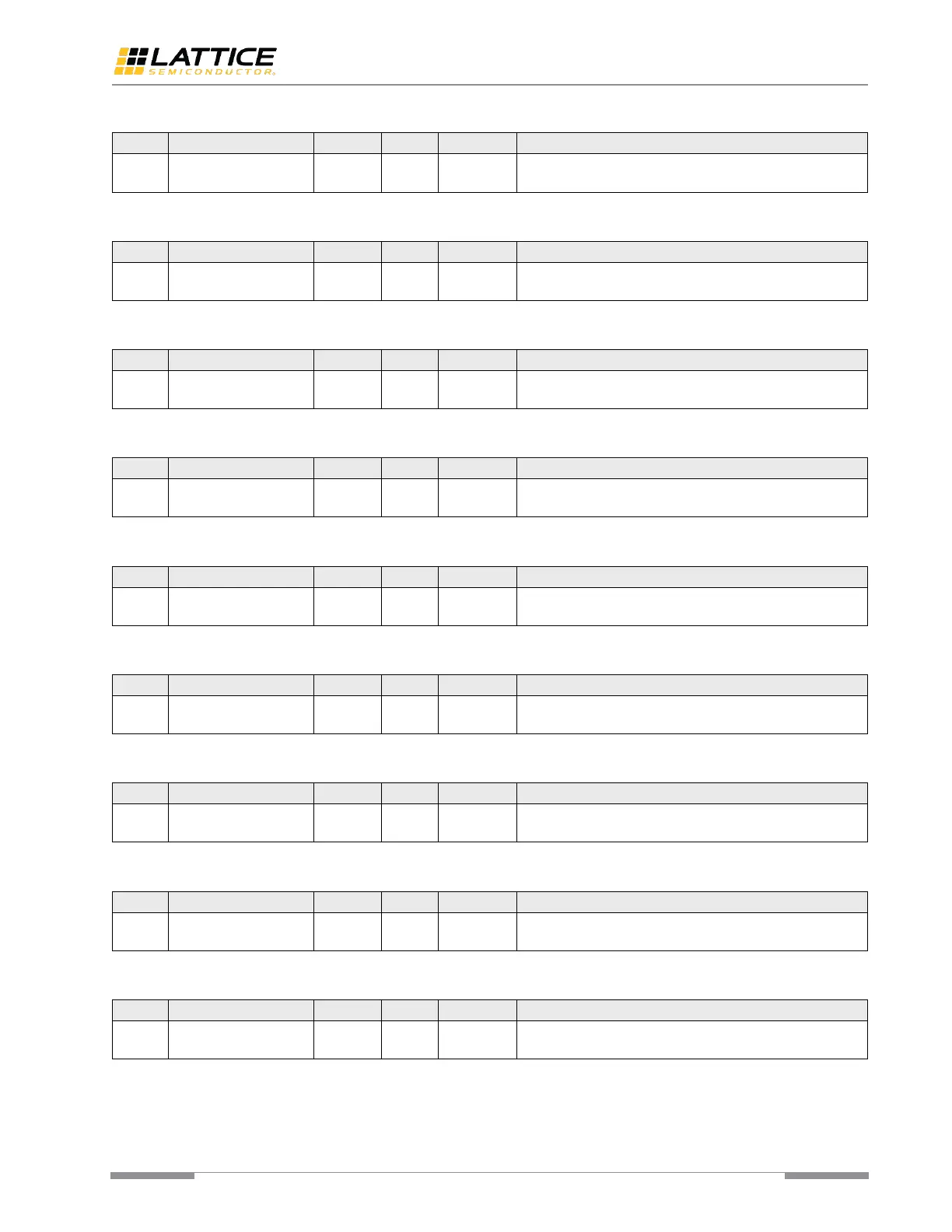

Table A. 119. 10GBASE-R Test Pattern Seed B Byte 7 [rega1]

This register defines byte 7 of 10GBASE-R PCS test pattern

seed B.

Loading...

Loading...