CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 143

All rights reserved. CONFIDENTIAL

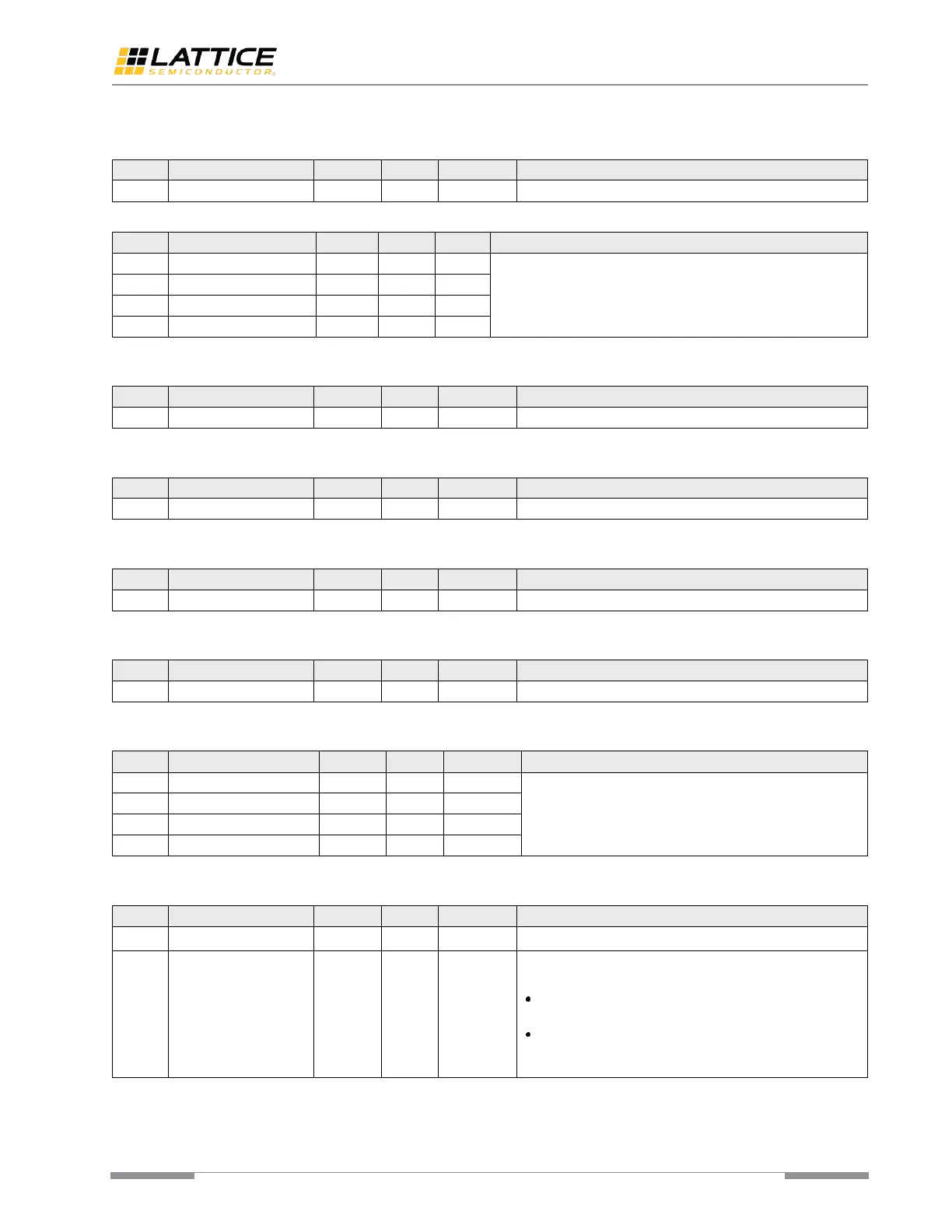

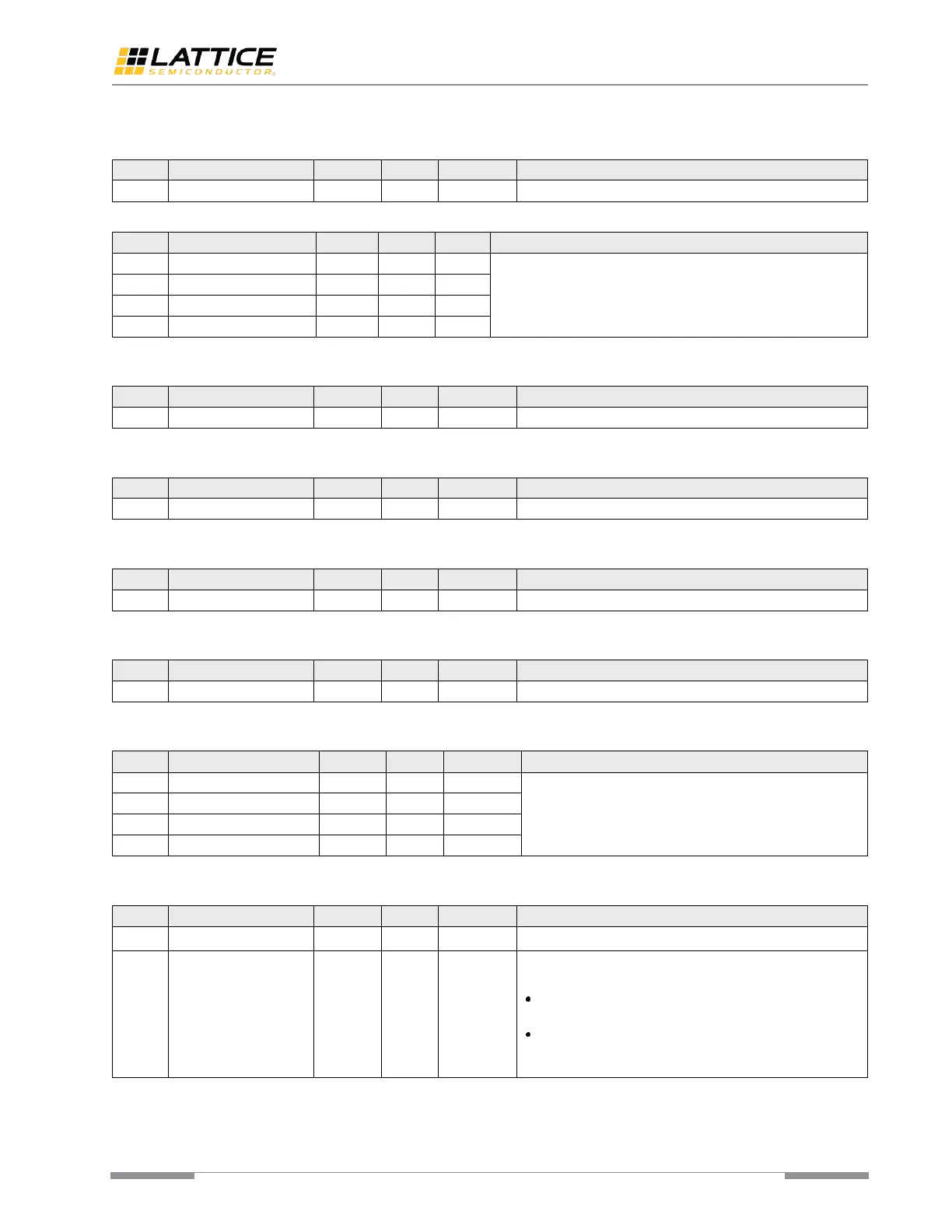

Table A. 72. Primary Lane Alignment Pattern Byte 3 [reg55]

Primary Lane Alignment Pattern Byte 3.

Table A. 73. Primary Lane Alignment Pattern Byte MSB [reg56]

Primary Lane Alignment Pattern MSB Register reflects the bits

9 to 8 of primary lane alignment pattern byte 3 to 0.

Table A. 74. Secondary Lane Alignment Pattern Byte 0 [reg57]

Secondary Lane Alignment Pattern Byte 0.

Table A. 75. Secondary Lane Alignment Pattern Byte 1 [reg58]

Secondary Lane Alignment Pattern Byte 1.

Table A. 76. Secondary Lane Alignment Pattern Byte 2 [reg59]

Secondary Lane Alignment Pattern Byte 2.

Table A. 77. Secondary Lane Alignment Pattern Byte 3 [reg5a]

Secondary Lane Alignment Pattern Byte 3.

Table A. 78. Secondary Lane Alignment Pattern Byte MSB [reg5b]

Secondary Lane Alignment Pattern MSB Register reflects

the bits 9 to 8 of secondary lane alignment pattern byte 3

to 0.

Table A. 79. Lane Alignment Pattern Mask Code [reg5c]

Lane Alignment Pattern mask code, bit 3 for pattern byte

3 and bit 0 for pattern byte 0.

1’b1 – the corresponding byte of lane alignment

pattern is ignored during alignment pattern matching.

1’b0 – the corresponding byte of lane alignment

pattern is not ignored during alignment pattern

matching.

Loading...

Loading...