CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 99

All rights reserved. CONFIDENTIAL

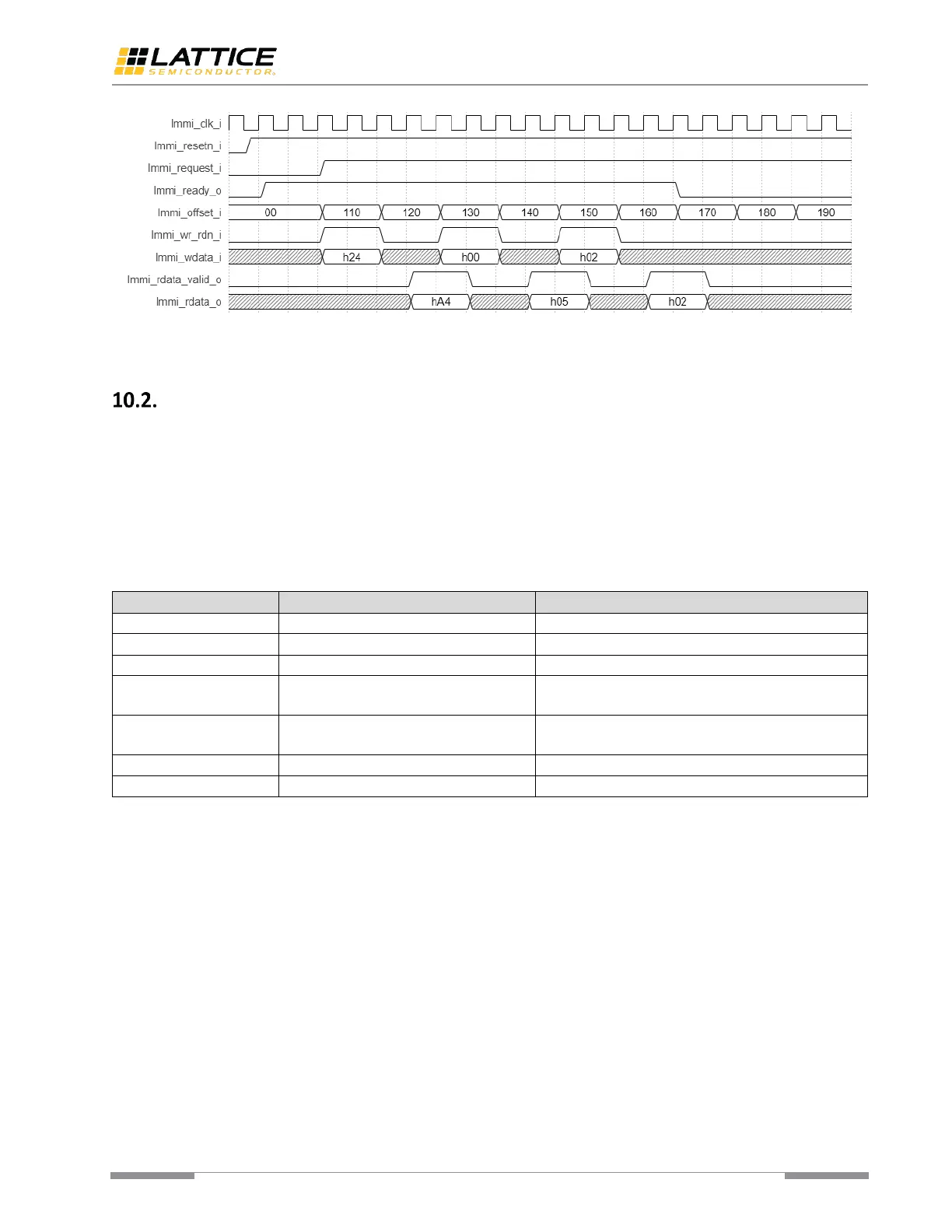

Figure 10.3. Back-to-Back Write and Read Transaction

Register Space

Each SerDes/PCS channel has independent register space which includes following category of registers:

Configuration registers

Control registers

Status registers

Status registers with clear-on-read

All register bits in Appendix A. Configure Registers are shown with bit7 as the significant bit on the left. Table 10.1

shows the abbreviations that are used to indicate what type of register access for each is supported.

Table 10.1. Access Type Definition

Loading...

Loading...