CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 151

All rights reserved. CONFIDENTIAL

1’b1 – Zeros data pattern.

1’b0 – LF data pattern.

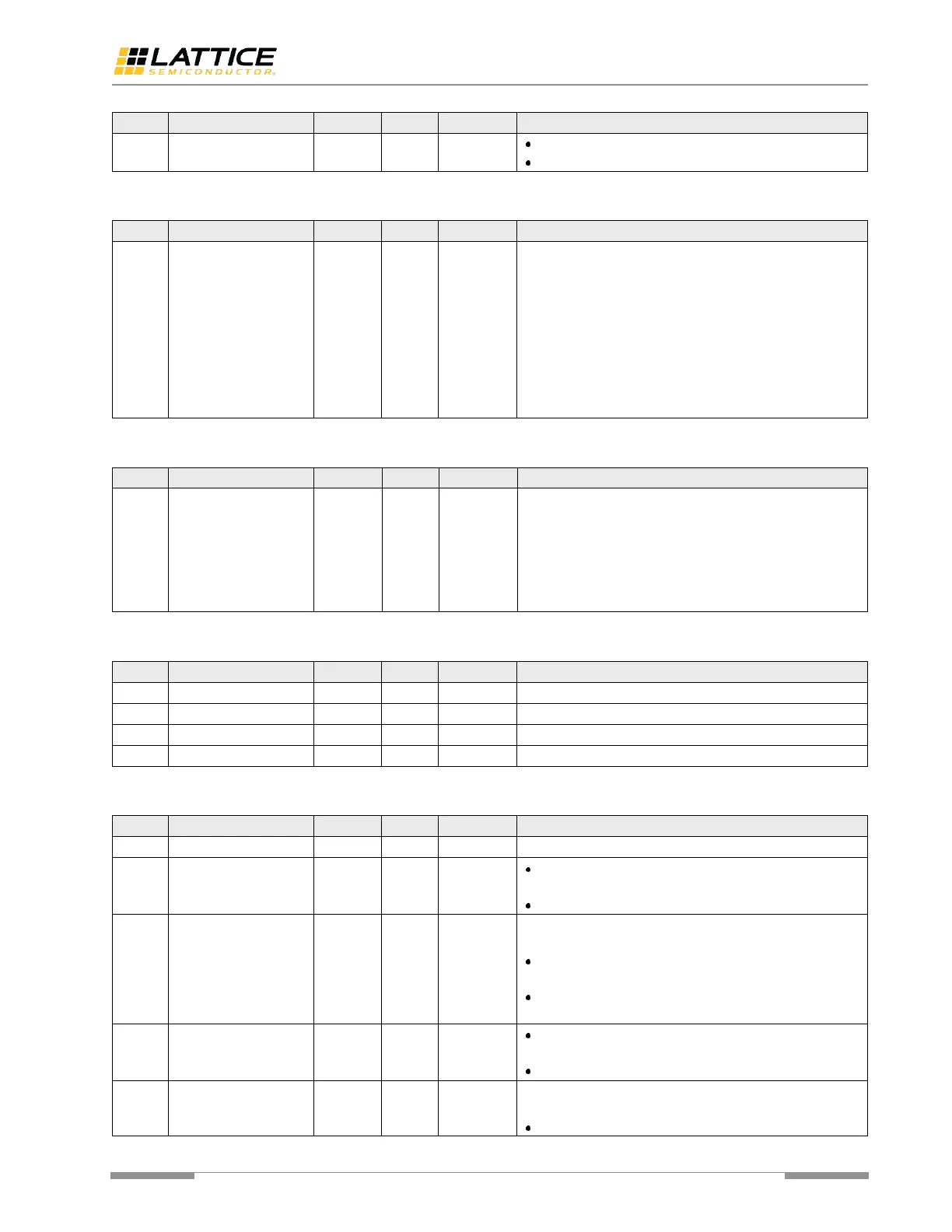

Table A. 122. 10GBASE-R Test Pattern Error Counter Byte 0 [rega4]

10GBASE-R Test Pattern Error Counter Byte 0 register

reflects the counter containing the number of errors

received during a pattern test. These bits are reset to all

zeros when the test-pattern error counter is read or upon

execution of the PCS reset. These bits are held at all ones

in the case of overflow. This counter counts either block

errors or bit errors depending on the test mode.

Note: When accessing this counter, must read the low

address byte (this register) first, then read the high

address byte (next register).

Table A. 123. 10GBASE-R Test Pattern Error Counter Byte 1 [rega5]

10GBASE-R Test Pattern Error Counter Byte 1 register

reflects the counter containing the number of errors

received during a pattern test. These bits are reset to all

zeros when the test-pattern error counter is read or upon

execution of the PCS reset. These bits are held at all ones

in the case of overflow. This counter counts either block

errors or bit errors depending on the test mode.

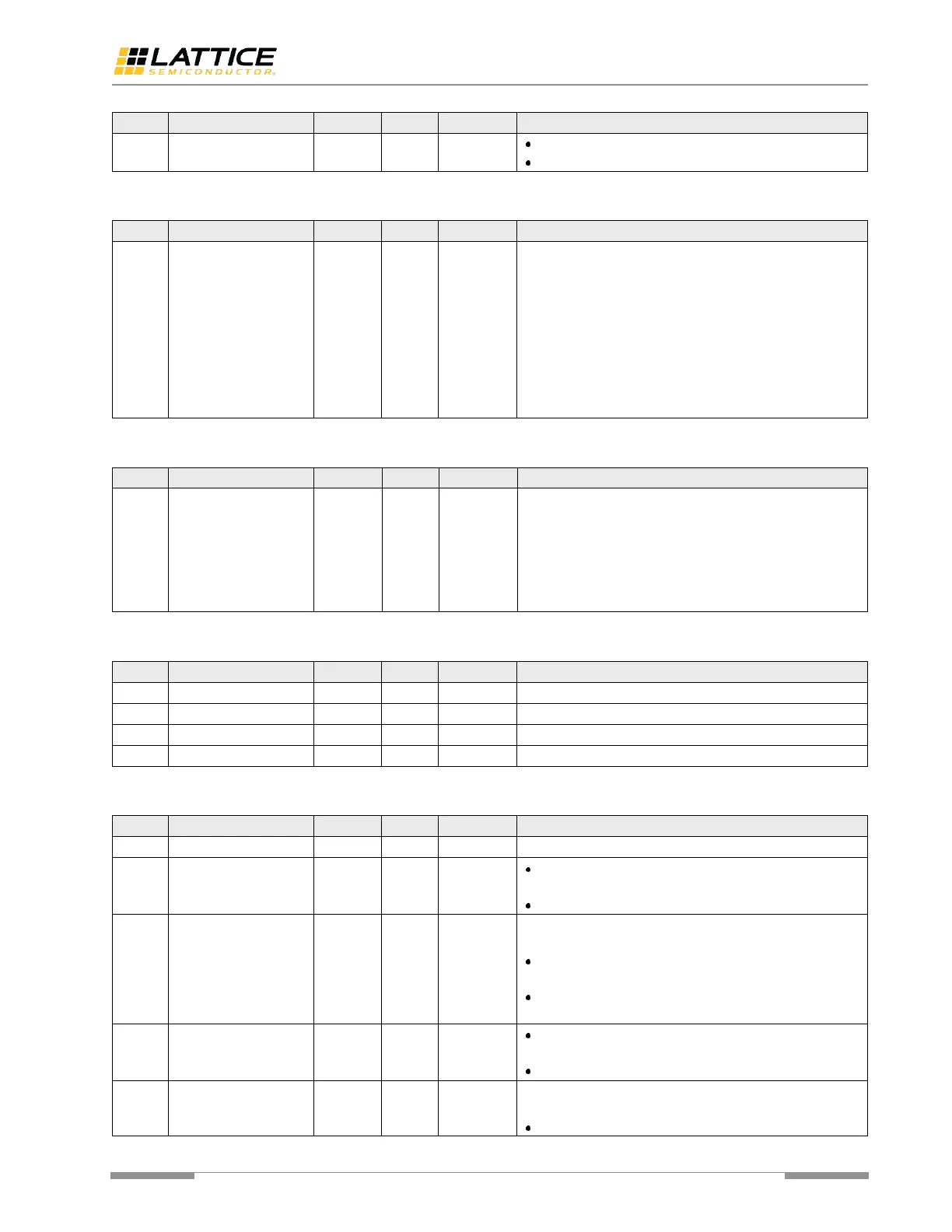

Table A. 124. PMA Control [regc6]

The value of pma_rxval signal.

The value of pma_ready signal.

The value of pma_phyrdy signal.

Table A. 125. PMA Control [regc7]

1’b1 – use bit[2] of this register to override the PMA

control signal "epcs_rstn".

1’b0 – use "pma_rstn" to drive "epcs_rstn".

If bit[3] of this register is set to "1", use this bit to override

the PMA control signal "epcs_rstn".

1’b1 – drive "epcs_rstn" high if "pma_rstn_ovrd" is set

to "1".

1’b0 – drive "epcs_rstn" low if "pma_rstn_ovrd" is set

to "1".

1’b1 – use bit[0] of this register to override the PMA

control signal "epcs_txval".

1’b0 – use "pma_txval" to drive "epcs_txval".

If bit[1] of this register is set to "1", use this bit to override

the PMA control signal "epcs_txval".

1’b1 – drive "epcs_txval" high if "txval_ovrd" is set to

Loading...

Loading...