CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

152 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

"1".

1’b0 – drive "epcs_txval" low if "txval_ovrd" is set to

"1".

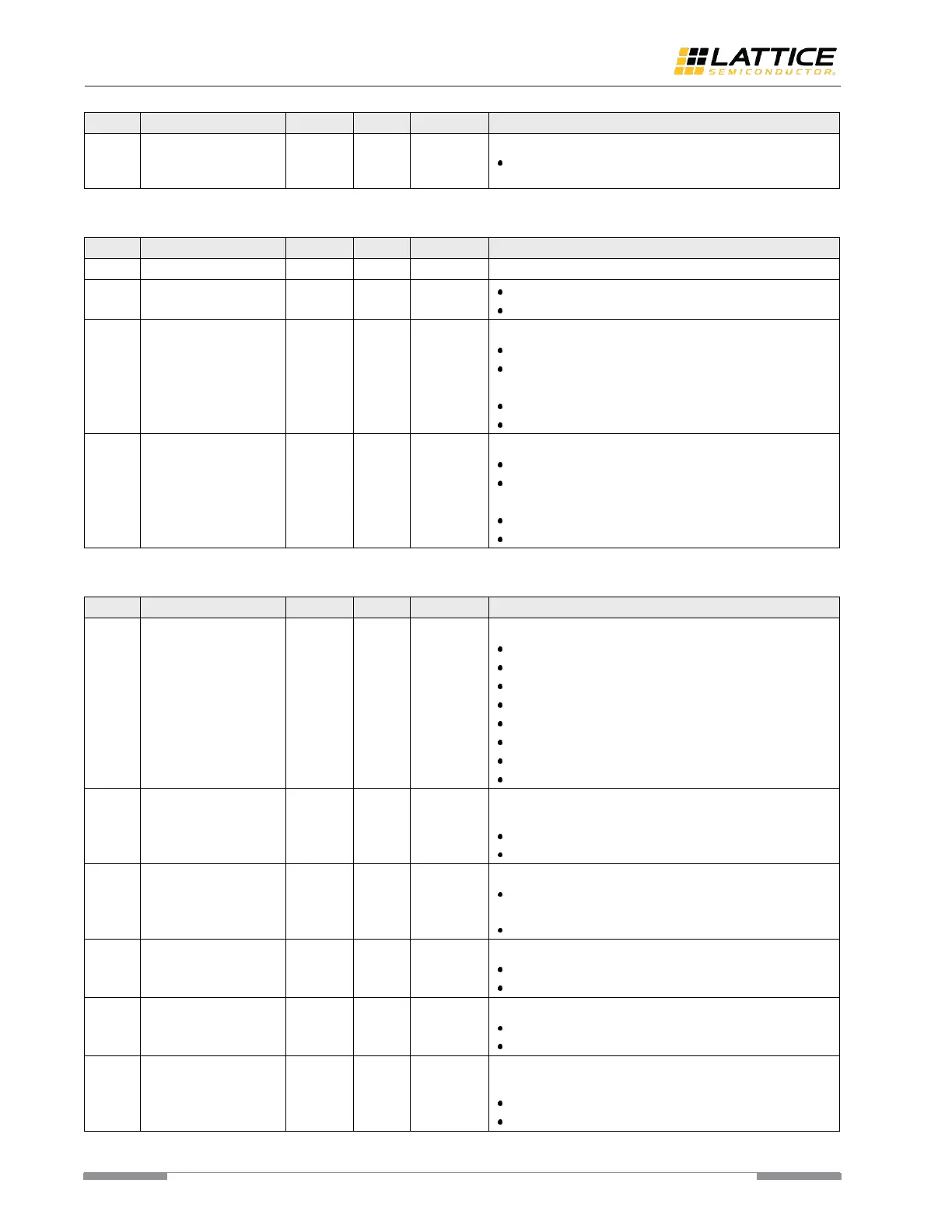

Table A. 126. Loopback Mode Control [rege0]

1’b1 – enable 64B/66B PCS loopback B.

1’b0 – do not enable 64B/66B PCS loopback B.

In 8B/10B PCS mode:

1’b1 – enable far end parallel loopback.

1’b0 – do not enable far end parallel loopback.

In 64B/66B PCS mode:

1’b1 – enable loopback C.

1’b0 – do not enable loopback C.

In 8B/10B PCS mode:

1’b1 – enable near end parallel loopback.

1’b0 – do not enable parallel loopback.

In 64B66B PCS mode:

1’b1 – enable loopback A.

1’b0 – do not enable loopback A.

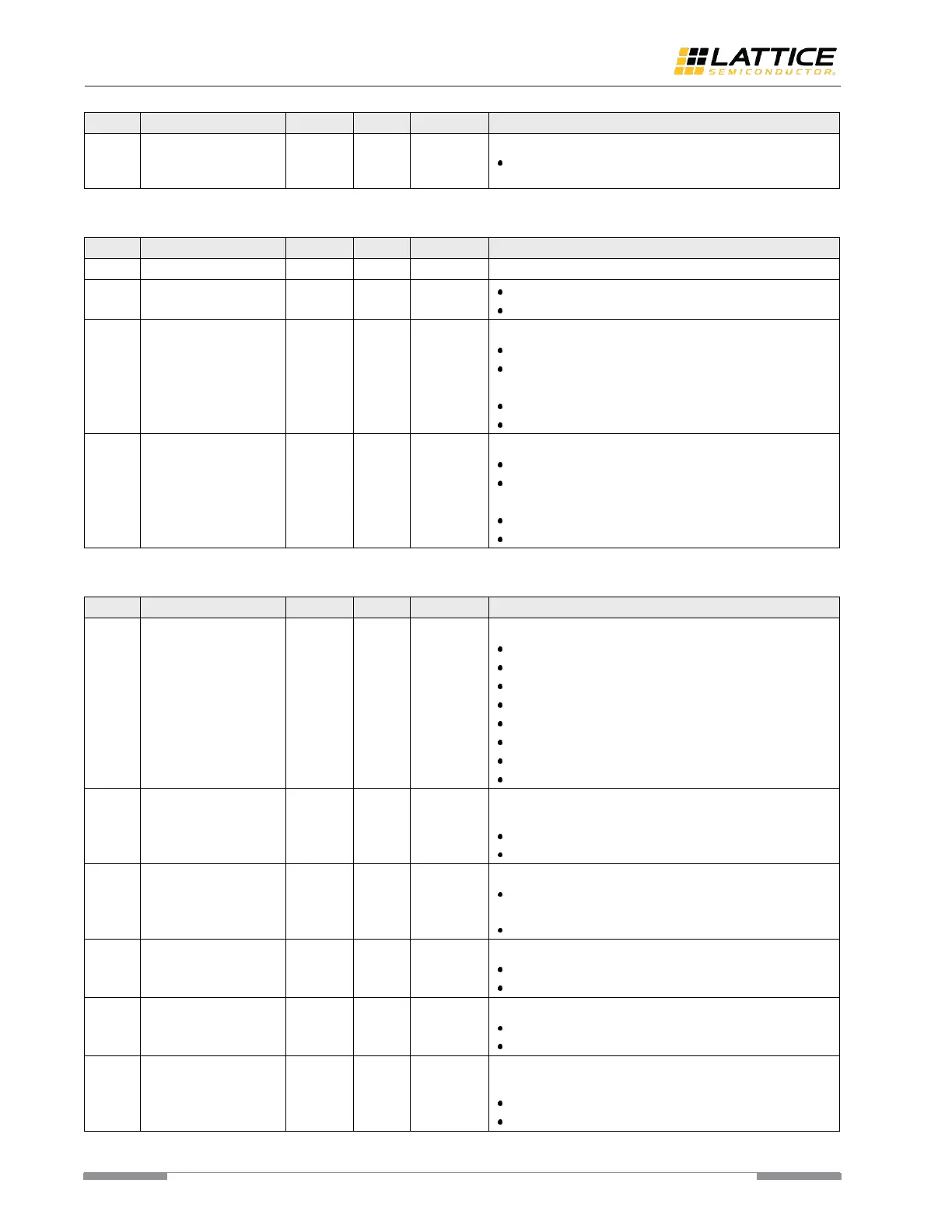

Table A. 127. MPCS BIST Control 0 [rege1]

BIST Pattern Selection. Specifies the selected BIST Pattern.

3’b111 – Alternate Constant Values 1 and 2

3’b110 – Constant Value 2

3’b101 – Constant Value 1

3’b100 – PRBS15

3’b011 – PRBS31

3’b010 – PRBS23

3’b001 – PRBS11

3’b000 – PRBS7

Data receive selector. Specifies the selector where the

data is to be received.

1’b1 – data from after 8B/10B decoder.

1’b0 – data from PMA.

Bypass Transmit gate.

1’b1 – force to send BIST data no matter the head is

found or not.

1’b0 – start to send BIST data after finding the head.

BIST bus width selector.

1’b1 – 8-bit BIST data.

1’b0 – 10-bit BIST data.

BIST mode. Specifies the BIST mode to be used.

1’b1 – Continuous BIST mode.

1’b0 – Timed BIST mode.

Enable MPCS BIST. Specifies the MPCS BIST is enabled or

disabled.

1’b1 – MPCS BIST is enabled

1’b0 – MPCS BIST is disabled

Loading...

Loading...