CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

146 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

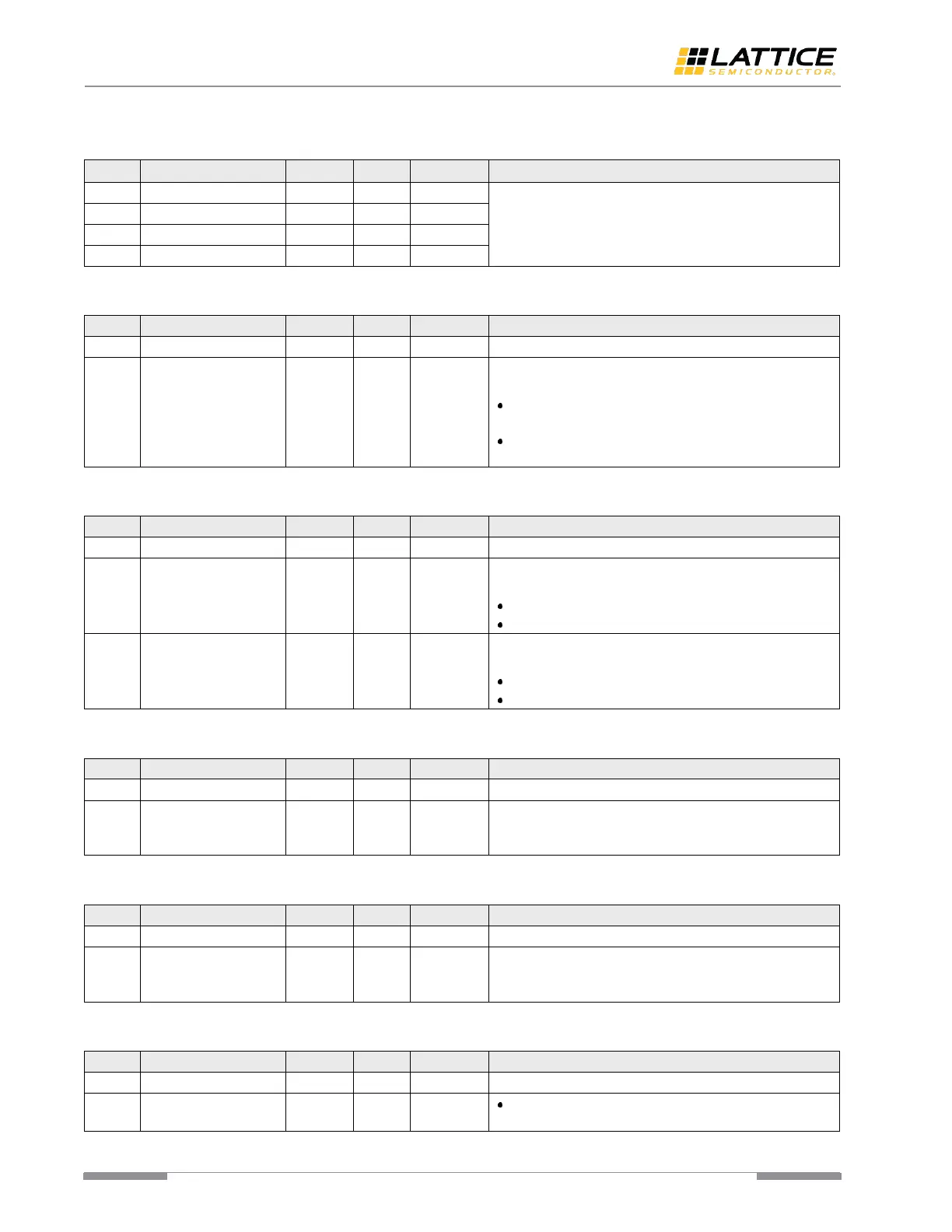

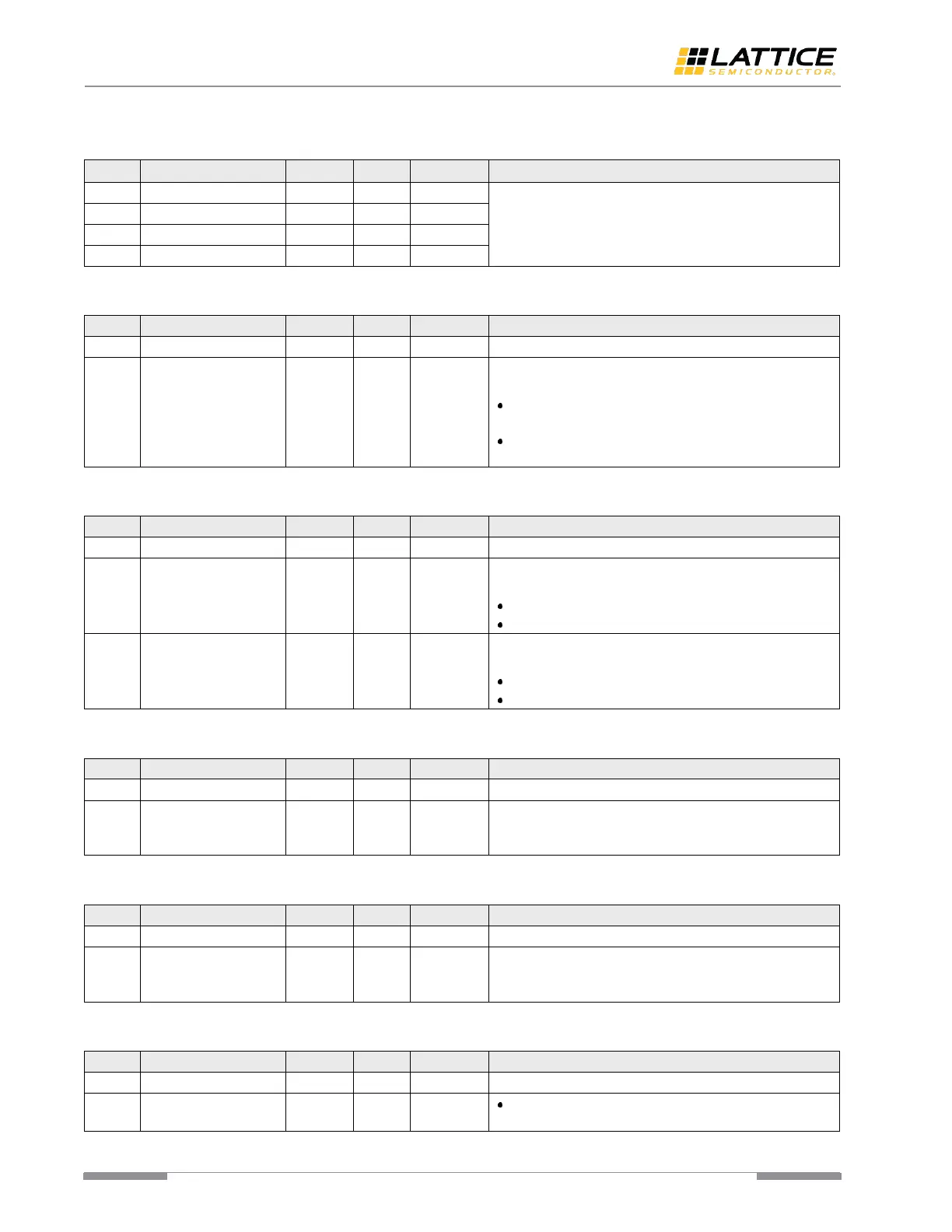

Table A. 93. Secondary SKIP Pattern MSB [reg6d]

Secondary SKIP Pattern MSB Register reflects the bits 9 to

8 of Secondary SKIP Pattern byte 3 to 0.

Table A. 94. SKIP Pattern Mask Code [reg6e]

SKIP Pattern Mask Code. Specifies whether the SKIP

Pattern is ignored or not.

1’b1 – The corresponding byte of SKIP pattern is

ignored during SKIP pattern matching.

1’b0 – The corresponding byte of SKIP pattern is not

ignored during SKIP pattern matching.

Table A. 95. 64B/66B PCS Tx Path Control [reg80]

Enable 64B/66B Encoder. Specifies the 64B/66B Encoder is

enabled or disabled.

1’b1 – 64B/66B Encoder is disabled.

1’b0 – 64B/66B Encoder is enabled.

Enable 64B/66B Scrambler. Specifies the 64B/66B

Scrambler is enabled or disabled.

1’b1 – 64B/66B Scrambler is disabled.

1’b0 – 64B/66B Scrambler is enabled.

Table A. 96. 64B/66B PCS Tx FIFO Almost Full Setting Control [reg81]

64B/66B Tx FIFO Almost Full. When the number of blocks

residing in the FIFO is more than this setting, the "almost

full" status is reported.

Table A. 97. 64B/66B PCS Tx FIFO Almost Empty Setting Control [reg82]

64B/66B Tx FIFO Almost Empty. When the number of

blocks residing in the FIFO is less than this setting, the

"almost empty" status is reported.

Table A. 98. 64B/66B PCS Rx Path Control [reg83]

1’b1 – Allow continuously delete sequence ordered set

when doing clock frequency compensation.

Loading...

Loading...