CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 115

All rights reserved. CONFIDENTIAL

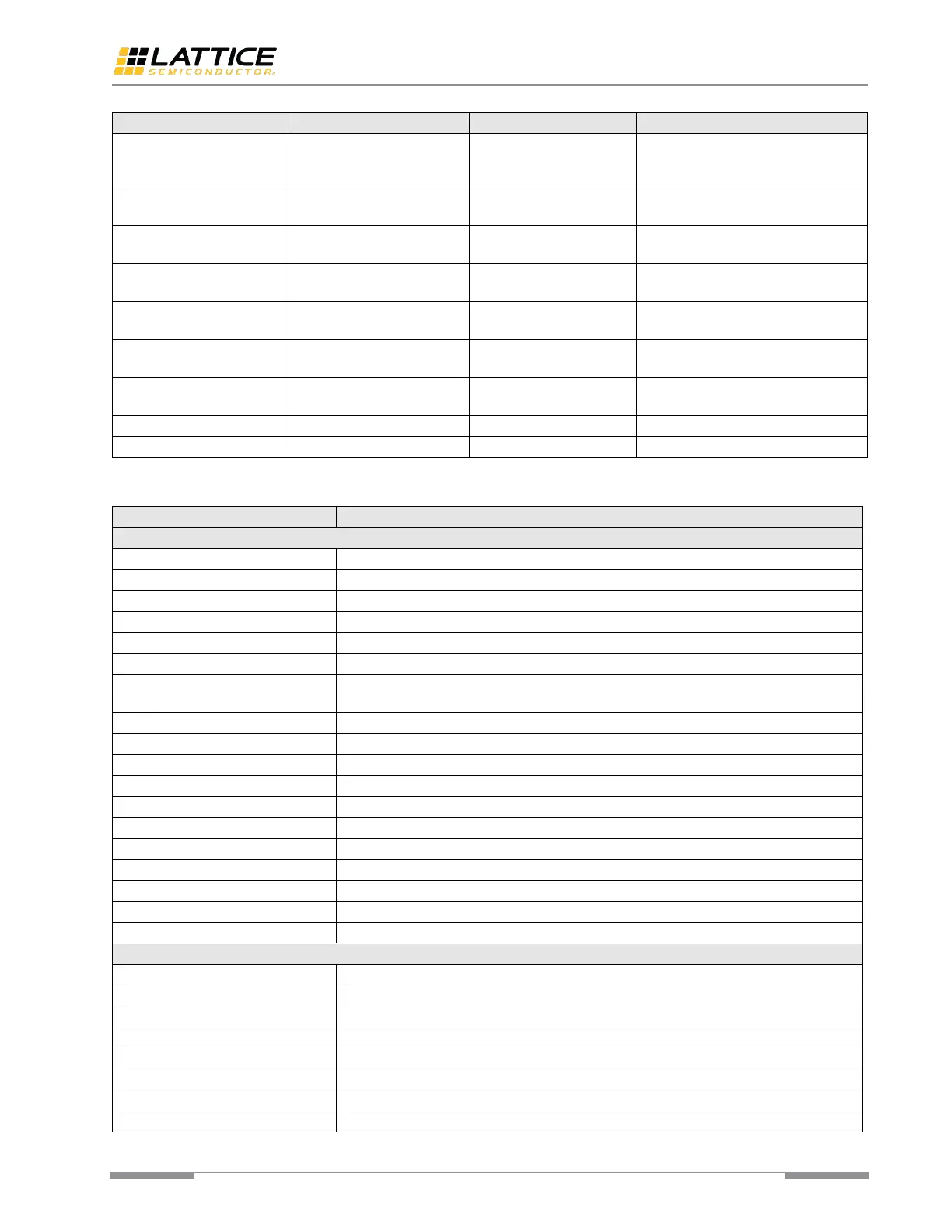

Dependency on Other Attributes

“6_SKEW”, “7_SKEW”,

“8_SKEW”, “9_SKEW”,

“10_SKEW”,

Primary Lane Alignment

Pattern Byte 0 (HEX)

Active if Lane Alignment ==

“ENABLED”

Primary Lane Alignment

Pattern Byte 1 (HEX)

Active if Lane Alignment ==

“ENABLED”

Primary Lane Alignment

Pattern Byte 2 (HEX)

Active if Lane Alignment ==

“ENABLED”

Primary Lane Alignment

Pattern Byte 3 (HEX)

Active if Lane Alignment ==

“ENABLED”

Active if Lane Alignment ==

“ENABLED”

Active if Lane Alignment ==

“ENABLED”

Near End Parallel Loopback

Far End Parallel Loopback

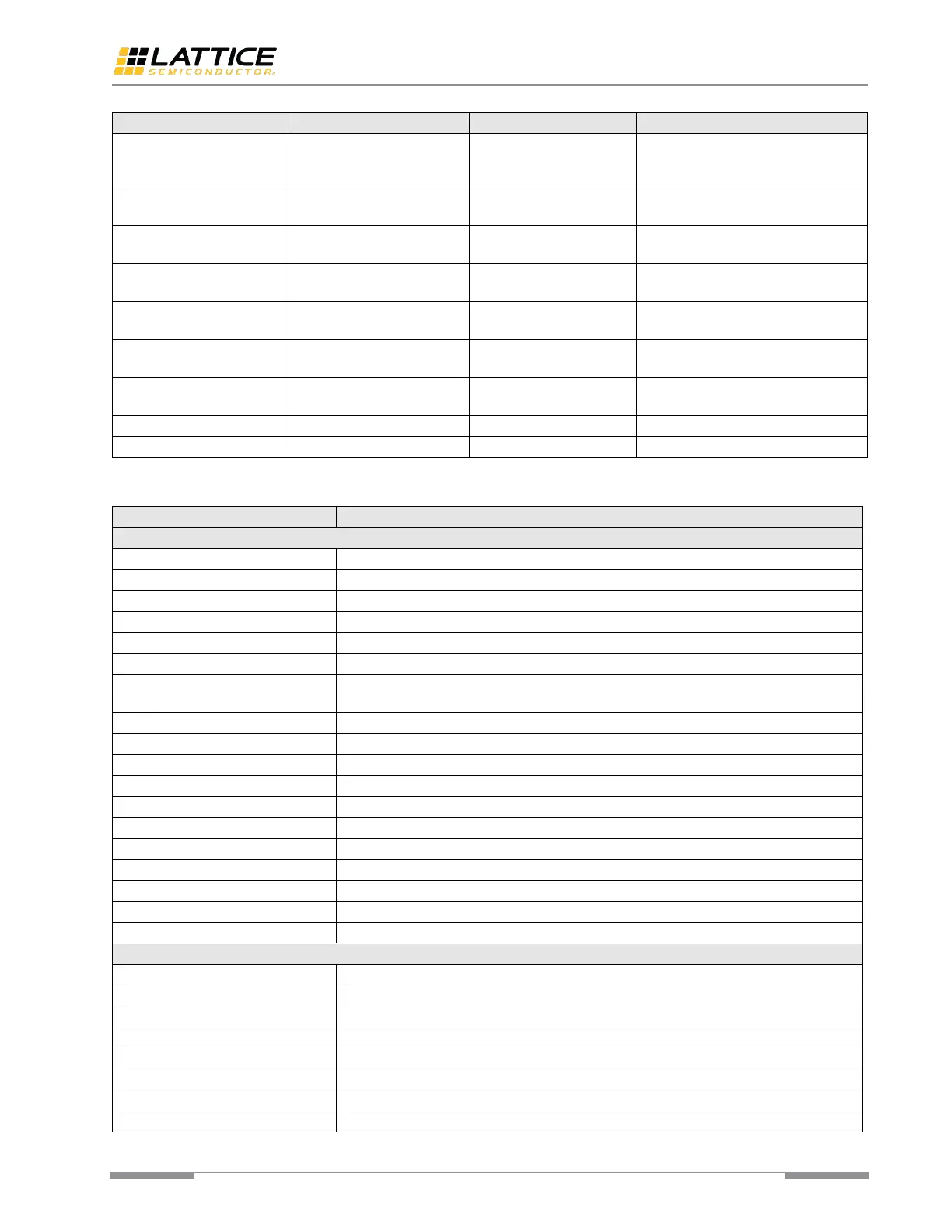

Table 14.3. Attributes Descriptions

Specifies the selected protocol of the MPCS Module, uses MPCS mode.

If enabled, MPCS Module is in EPCS mode.

Specifies the value of reg00. tx_src_ovrd.

Specifies the value of reg00. rx_src_ovrd.

Specifies the number of lane the user can use.

Specifies the first channel of the PCS instance.

Specifies the group name of the PCS instance. Aligned channels have the same group

name.

Specifies the selected mode, which can be “Rx_only”, “Tx_only” or “Rx_and_“Tx”.

Specifies the data rate of the selected Protocol in Gbps.

Specifies the assigned data rate for the dynamic changing.

Specifies the assigned data rate for the dynamic changing.

Specifies the assigned data rate for the dynamic changing.

Specifies the user bus width available for the selected Protocol.

Specifies the reference clock frequency of the selected Data Rate.

Specifies the use of internal reference clock from PCSREFMUX.

RefClk Selection for Quad0

Lists the reference clocks available for users.

External IO Pad RefClk for Quad0

Lists the available IO Pad Reference Clocks.

Refer to Table 5.4 for more information about this attribute.

Specifies the value of reg80. src_64b66b_dis.

Specifies the value of reg80. end_64b66b_dis.

64b66b RX FIFO Almost Full

Specifies the value of reg81. tx_fifo_af.

64b66b TX FIFO Almost Empty

Specifies the value of reg82. tx_fifo_ae.

Specifies the value of reg83. descr_64b66b_dis.

Specifies the value of reg83. dec_64b66b_dis.

Clock Frequency Compensation

Specifies the value of reg83. ctc_64b66b_dis.

Specifies the value of reg83. balign_64b66b_dis.

Loading...

Loading...