CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 21

All rights reserved. CONFIDENTIAL

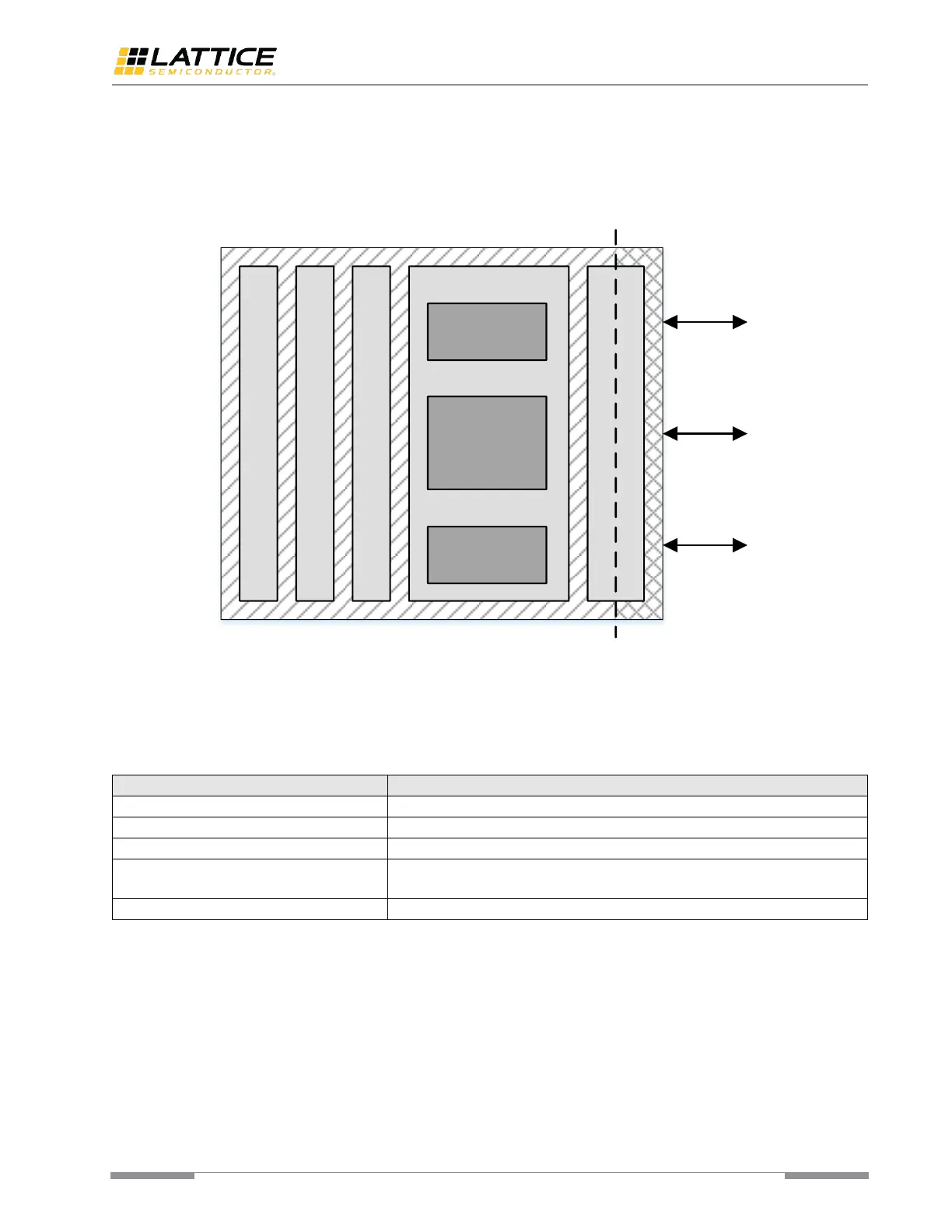

Express PCS block using the PIPE interface with up to 128-bit data width. The Link Layer block operates at the clock

frequency of 250 MHz, while the user interface is at 125 MHz in Gen1/Gen2 speed and 250 MHz in Gen3 speed. The

user interface, TLP interface, can be from 32 bits up to 128 bits wide depending on the core configuration. 32 bits of

the TLP interface is used for ×1 mode, 64 bits of TLP interface is used for ×2 mode, and 128 bits of the TLP interface is

used for ×4 mode.

PMA (SERDES) Quad

PCI Express PCS Quad

PCI Express Link Layer Quad

PCI Express Link

Layer x1 Core

PCI Express Link

Layer x4 Core

Configuration

Space Registers

(x1 + x4)

Buffer

250 MHz

250 MHz for Gen

3

125 MHz for Gen

2/Gen1

32 bits UCFG x4

32 bits TLP (x1)

64 bits TLP (x2)

128 bits TLP (x4)

32 bits LMMI x4

PMA Controller

Figure 5.3. PCI Express Hard IP Architecture

Each PCI Express Link Layer Quad can be configured as x4 mode, x2 mode, x1 mode, x2_x1 mode and x1_x1 mode. In

x2_x1 mode, the Link Layer Quad can support two independent PCI Express applications, one in ×2 mode and the other

in ×1 mode. Table 5.4 describes the SerDes/PCS lane mapping details.

Table 5.4. PCI Express Link Layer Quad Lane Mapping

Lane 0 and Lane 1 are used.

Lane 0 and Lane 1 are used for ×2.

Lane 3 is used for ×1.

Lane 0 and Lane 3 are used for ×1.

Figure 5.4 shows the PCI Express Link Layer block functional diagram. For more detailed information on CertusPro-NX

PCI Express features, function descriptions, and IP usage, refer to CertusPro-NX PCI Express Hardened IP Core User

Guide (FPGA-IPUG-XXXXX).

Loading...

Loading...