CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 145

All rights reserved. CONFIDENTIAL

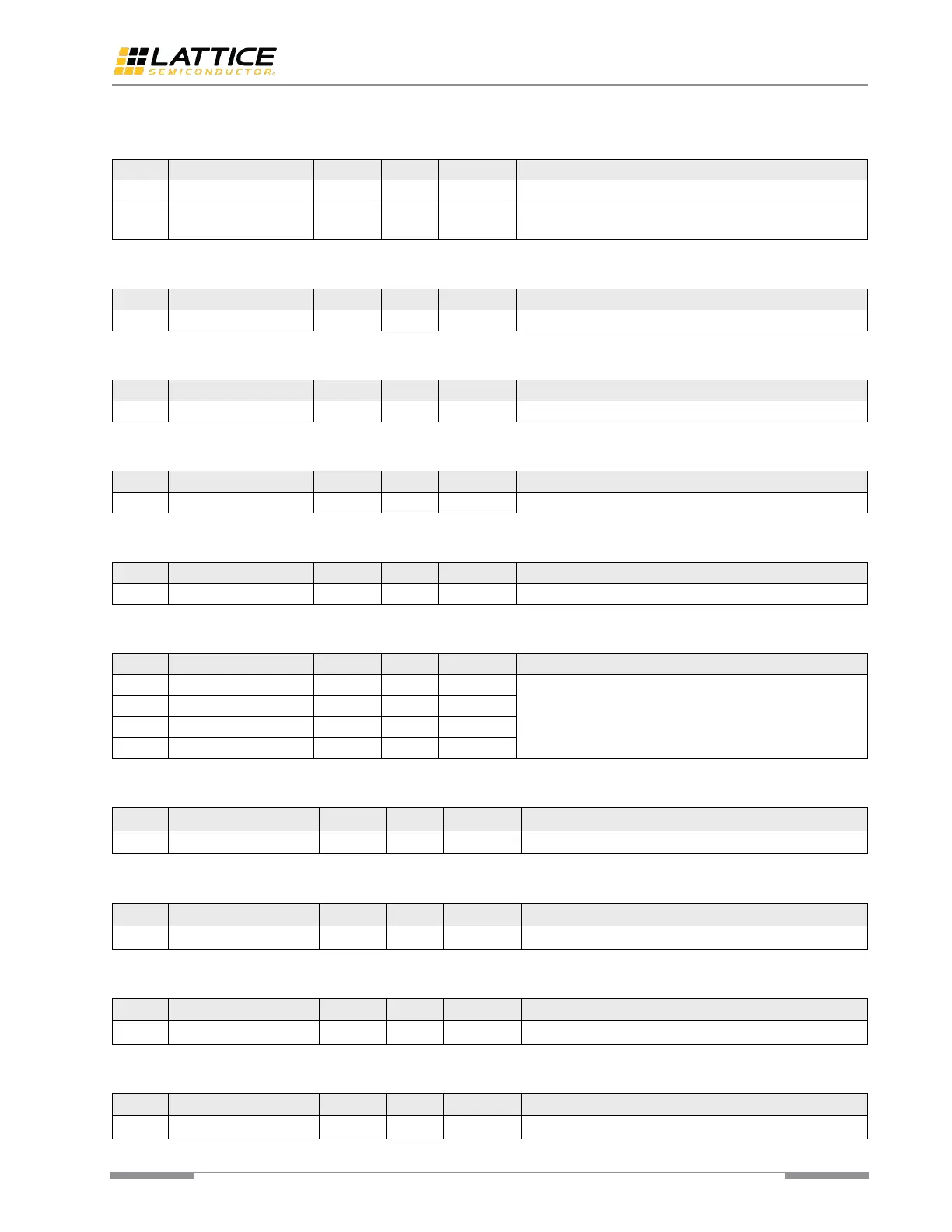

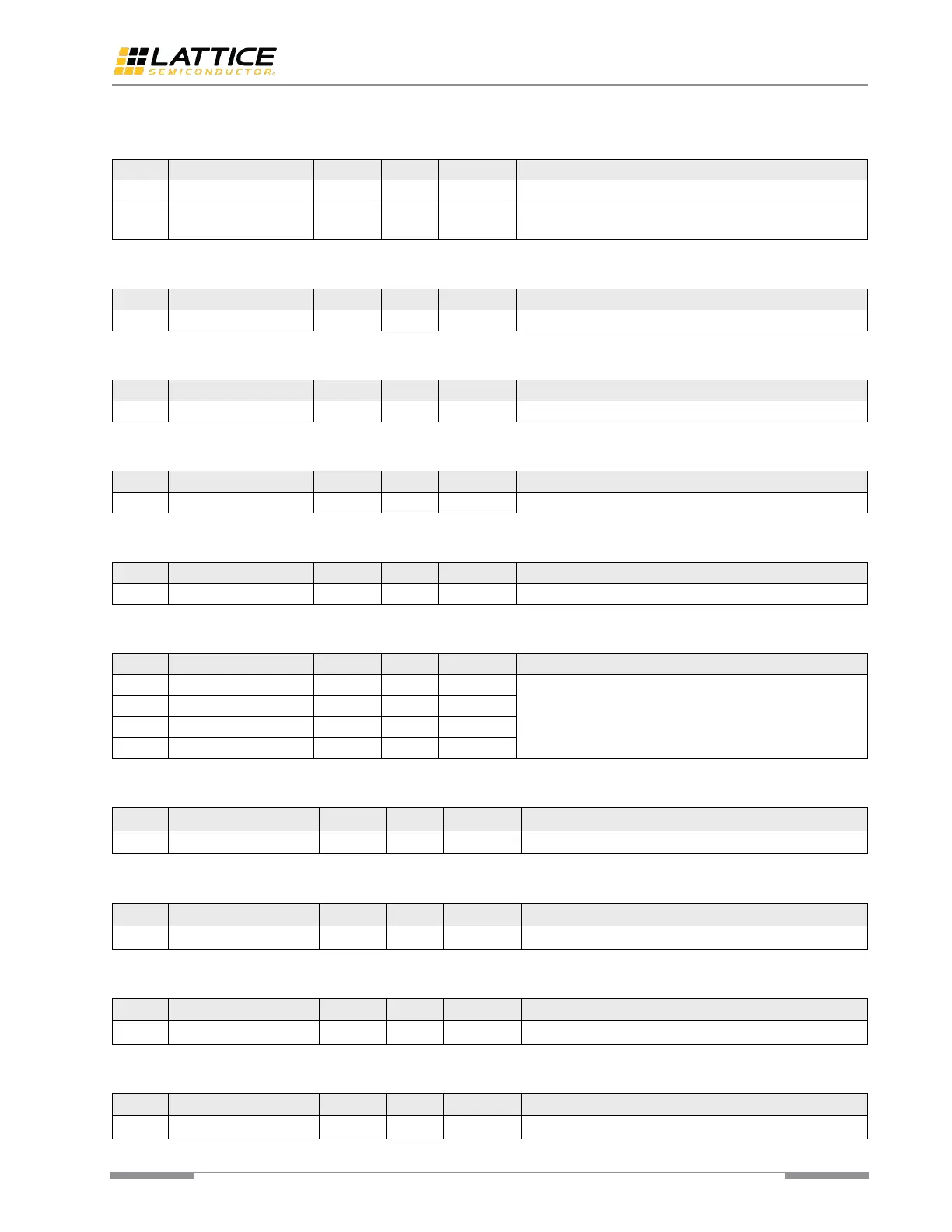

Table A. 83. Elastic FIFO Low Water Line [reg63]

Specifies the Clock Compensation FIFO low water line.

Mean is 5’b10000.

Table A. 84. Primary SKIP Pattern Byte 0 [reg64]

Primary SKIP Pattern Byte 0.

Table A. 85. Primary SKIP Pattern Byte 1 [reg65]

Primary SKIP Pattern Byte 1.

Table A. 86. Primary SKIP Pattern Byte 2 [reg66]

Primary SKIP Pattern Byte 2.

Table A. 87. Primary SKIP Pattern Byte 3 [reg67]

Primary SKIP Pattern Byte 3.

Table A. 88. Primary SKIP Pattern MSB [reg68]

Primary SKIP Pattern MSB Register reflects the bits 9 to 8

of Primary SKIP Pattern byte 3 to 0.

Table A. 89. Secondary SKIP Pattern Byte 0 [reg69]

Secondary SKIP Pattern Byte 0.

Table A. 90. Secondary SKIP Pattern Byte 1 [reg6a]

Secondary SKIP Pattern Byte 1.

Table A. 91. Secondary SKIP Pattern Byte 2 [reg6b]

Secondary SKIP Pattern Byte 2.

Table A. 92. Secondary SKIP Pattern Byte 3 [reg6c]

Secondary SKIP Pattern Byte 3.

Loading...

Loading...