CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

64 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

User logic can implement lane alignment state machine to monitor the alignment status and control Lane Aligner

module to perform re-alignment operation once loss of lane alignment is detected by user logic.

64B/66B PCS

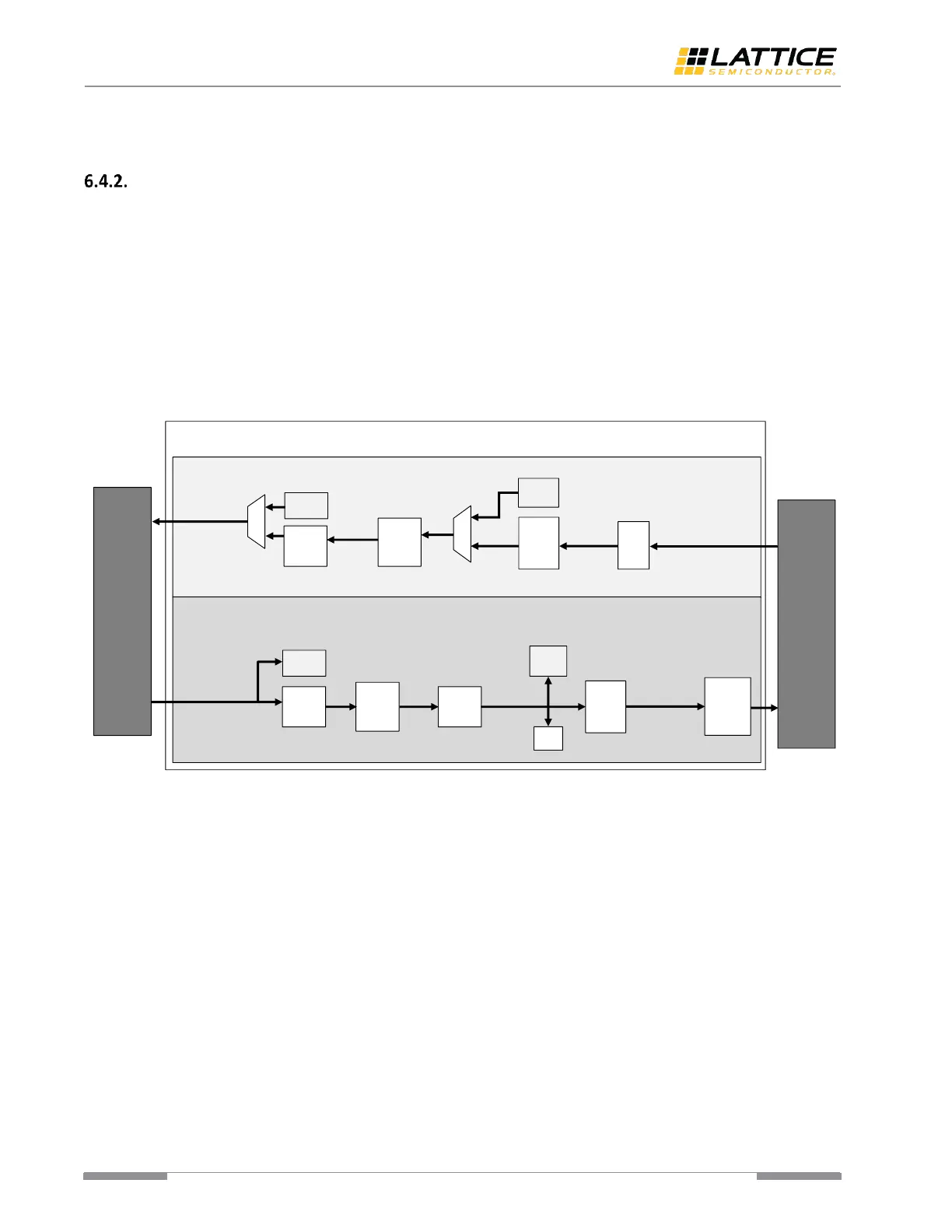

Figure 6.24 shows the block diagram of the 64B/66B PCS inside MPCS channel. This block implements the 10GBASE-R

PCS defined by IEEE802.3, which contains following sub-blocks:

Tx Gear Box and Rx Gear Box

PRBS Generator and Checker

Scrambler and Descrambler

PRD Pattern Generator and Checker

64B/66B Encoder and Decoder

Block Aligner

BER Monitor

Tx FIFO and Rx FIFO

Figure 6.24. 64B/66B PCS Channel Block Diagram

6.4.2.1. Data Bus Description

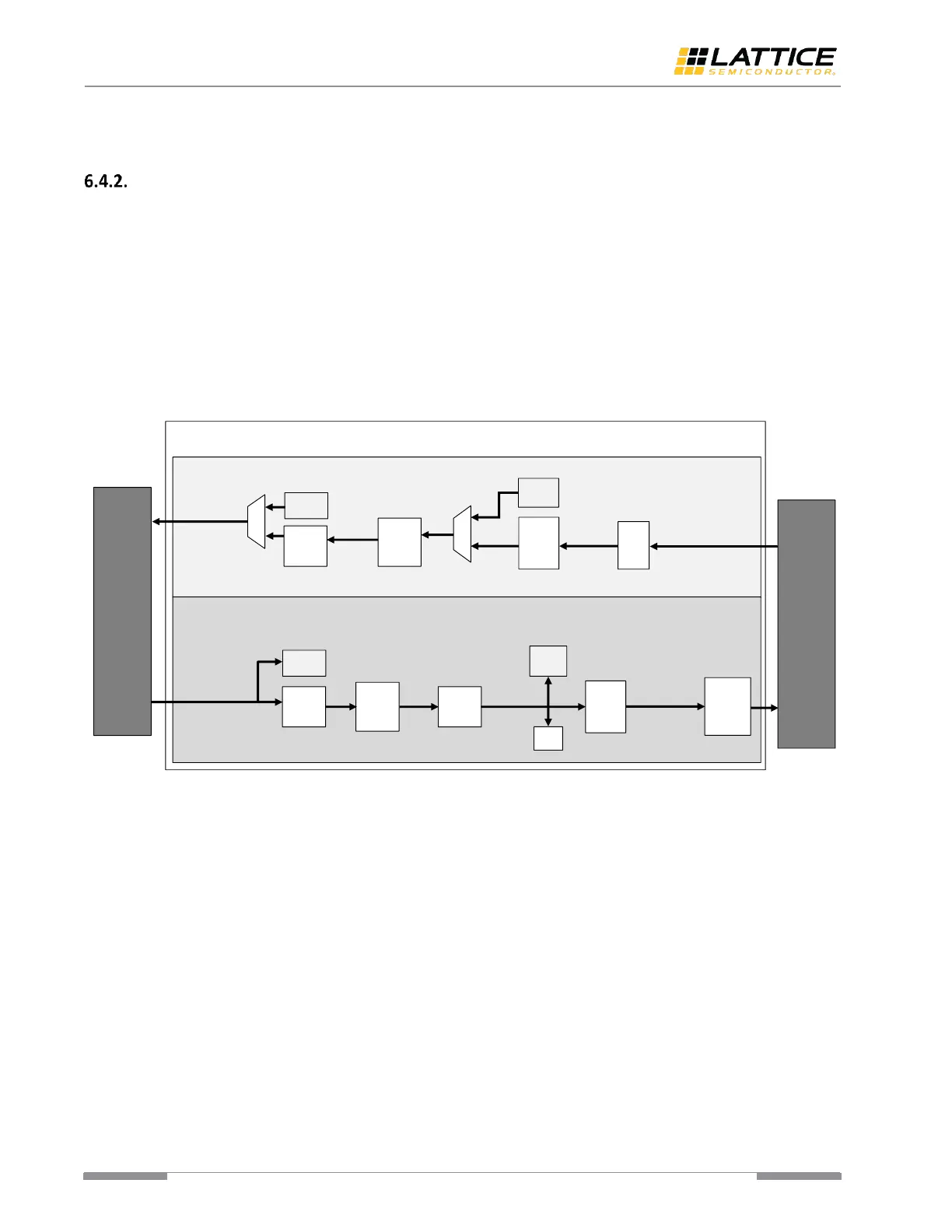

The 10 Gigabit Media Independent Interface (XGMII) is a Double Data Rate (DDR) interface between MAC and PCS,

defined by IEEE802.3 specification. CertusPro-NX device implements a Single Data Rate (SDR) MPCS-Fabric interface to

replace the standard XGMII, considering that it is difficult to implement the DDR interface with FPGA fabric. Figure 6.25

shows the comparison between XGMII and CertusPro-NX MPCS- Fabric interface.

Loading...

Loading...