CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

140 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

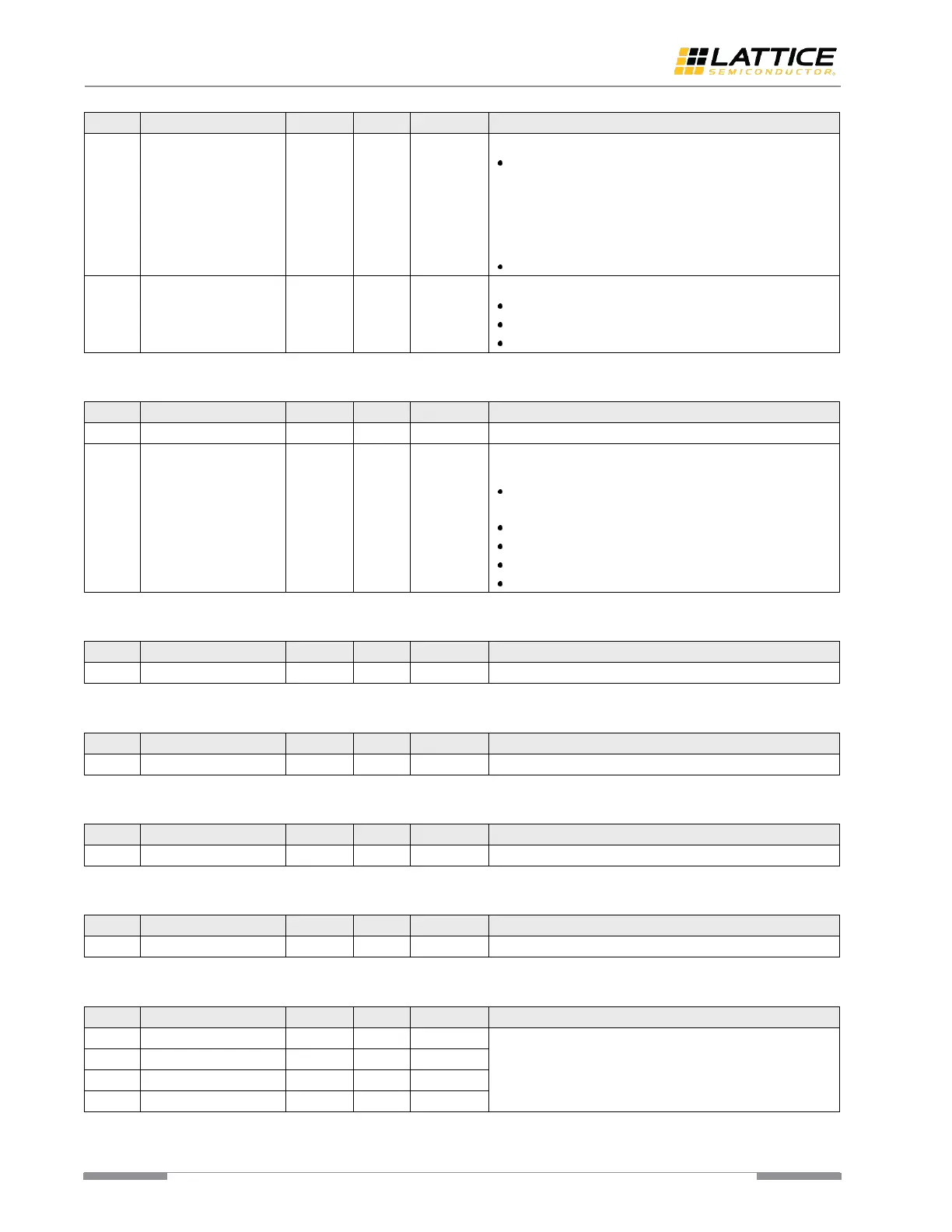

check is enabled or disabled.

1’b1 – the first byte of sync_det pattern must appear

on N-byte boundary, where N is the sync_det pattern

length defined by sync_ptn_len register. Once a

sync_det pattern is detected, the sync_det FSM applies

this creation to the validity check of subsequent

incoming data.

1’b0 – disable the sync detect pattern alignment check.

Pattern Length. Specifies the length of the pattern.

2’b1x – the length is 4.

2’b01 – the length is 2.

2’b00 – the length is 1.

Table A. 51. Number of Bit Slipped during Word Alignment [reg3e]

Code Group Length. Specifies the length of the code

group.

5’b10011 – 19 bits are slipped. 19 is the maximum bit

number.

…

5’b00010 – 2 bits are slipped.

5’b00001 – 1 bit is slipped.

5’b00000 – there is no bit slipped.

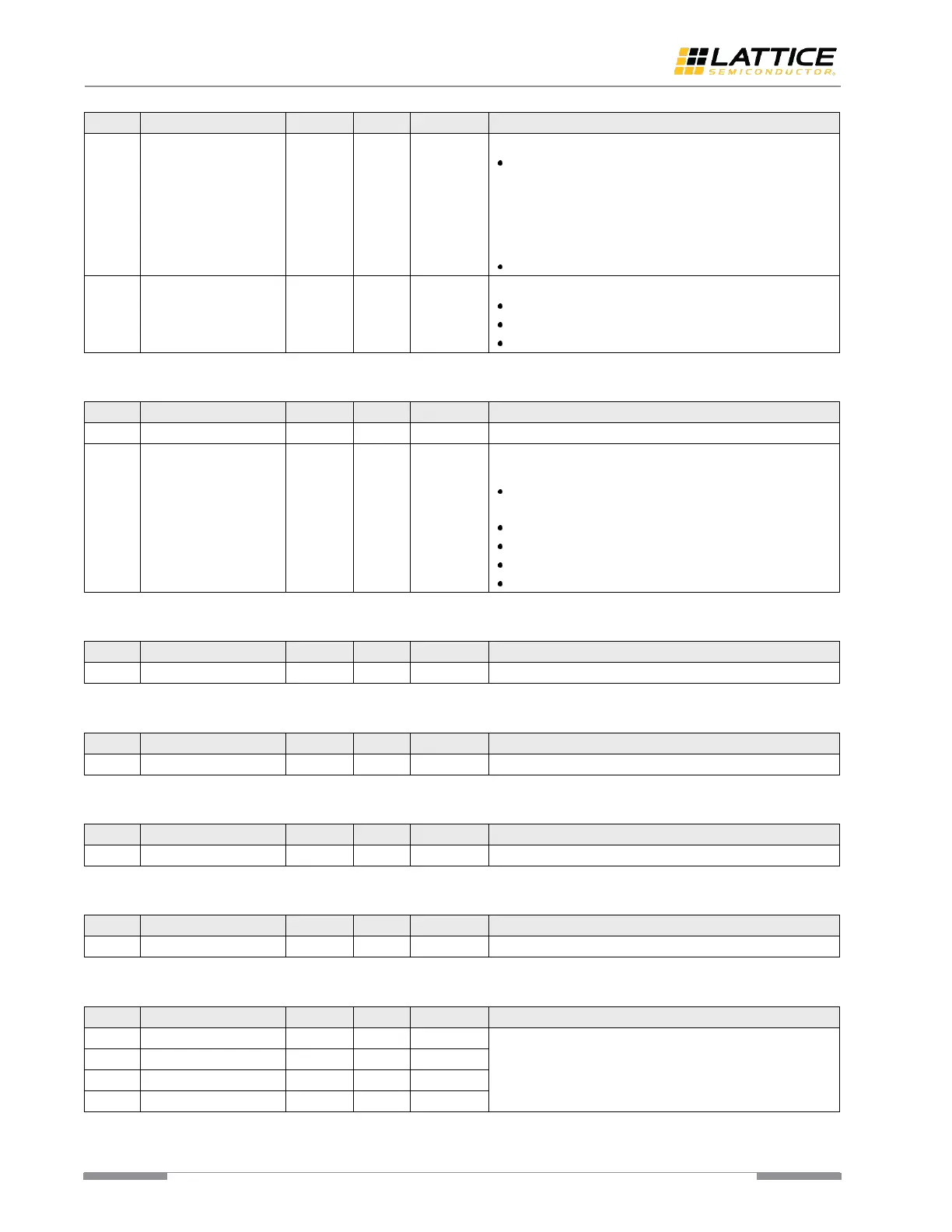

Table A. 52. Primary Sync_Det Pattern Byte 0 [reg3f]

Primary Sync_Det Pattern Byte 0.

Table A. 53. Primary Sync_Det Pattern Byte 1 [reg40]

Primary Sync_Det Pattern Byte 1.

Table A. 54. Primary Sync_Det Pattern Byte 2 [reg41]

Primary Sync_Det Pattern Byte 2.

Table A. 55. Primary Sync_Det Pattern Byte 3 [reg42]

Primary Sync_Det Pattern Byte 3.

Table A. 56. Primary Sync_Det Pattern Byte MSB [reg43]

Primary Sync_Det Pattern MSB Register reflects the bits 9

to 8 of primary Sync_Det pattern byte 3 to 0.

Loading...

Loading...