CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 77

All rights reserved. CONFIDENTIAL

Table 7.4. Quad Clock

This clock is used for lane alignment across Quad boundary. It can drive multiple

Quads tx_lalign_clk tree in the application case where more than four lanes (and up

to twelve lanes) are combined to form a single link.

The source of this clock is always tx_pcs_clk from channel_0 of this Quad. This

introduces a usage limitation that channel_0 must always be included in

multiple-channel link.

This clock is used for lane alignment across Quad boundary. It can drive multiple

Quads rx_lalign_clk tree in the application case where more than four lanes (and up

to twelve lanes) are combined to form a single link.

The source of this clock is always rx_pcs_clk from channel_0 of this Quad. This

introduces a usage limitation that channel_0 must be included in the

multiple-channel link.

This clock is shared by two adjacent Quads. It can be used to drive local tx_lalign_clk

tree.

This clock is shared by two adjacent Quads. It can be used to drive local rx_lalign_clk

tree.

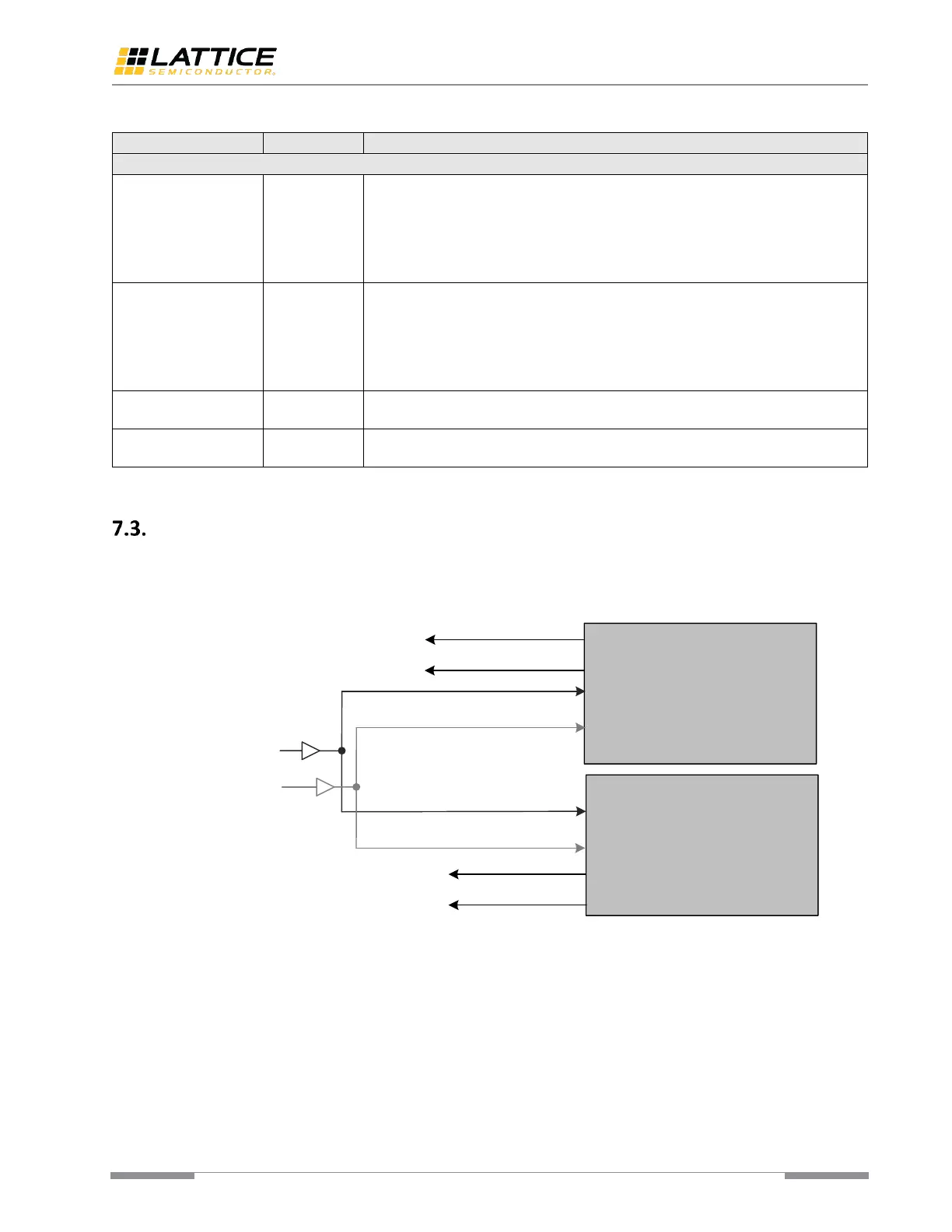

MPCS Quad-to-Quad Clock Connection

Figure 7.5 shows the clock connection between two adjacent Quads. The output alignment clocks (rx_lalign_clk_out

and tx_lalign_clk_out) from Quad 0 drive these two Quads (Quad 0 and Quad 1). Output clocks of Quad 1 are floating

and internally gated.

Quad 0

Quad 1

tx_lalign_clk_out[0]

rx_lalign_clk_out[0]

rx_lalign_clk_in[0]

rx_lalign_clk_in[1]

tx_lalign_clk_in[1]

tx_lalign_clk_in[0]

rx_lalign_clk_out[0]

tx_lalign_clk_out[0]

rx_lalign_clk_out[1]

tx_lalign_clk_out[1]

Floating

(internally gated)

Floating

(internally gated)

Figure 7.5. Two Quads Clock Connection

For single Quad applications, the output alignment clocks (rx_lalign_clk_out and tx_lalign_clk_out) are floating and

input clocks are tied low or high. Refer to Figure 7.6 for more details.

Loading...

Loading...