CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

138 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

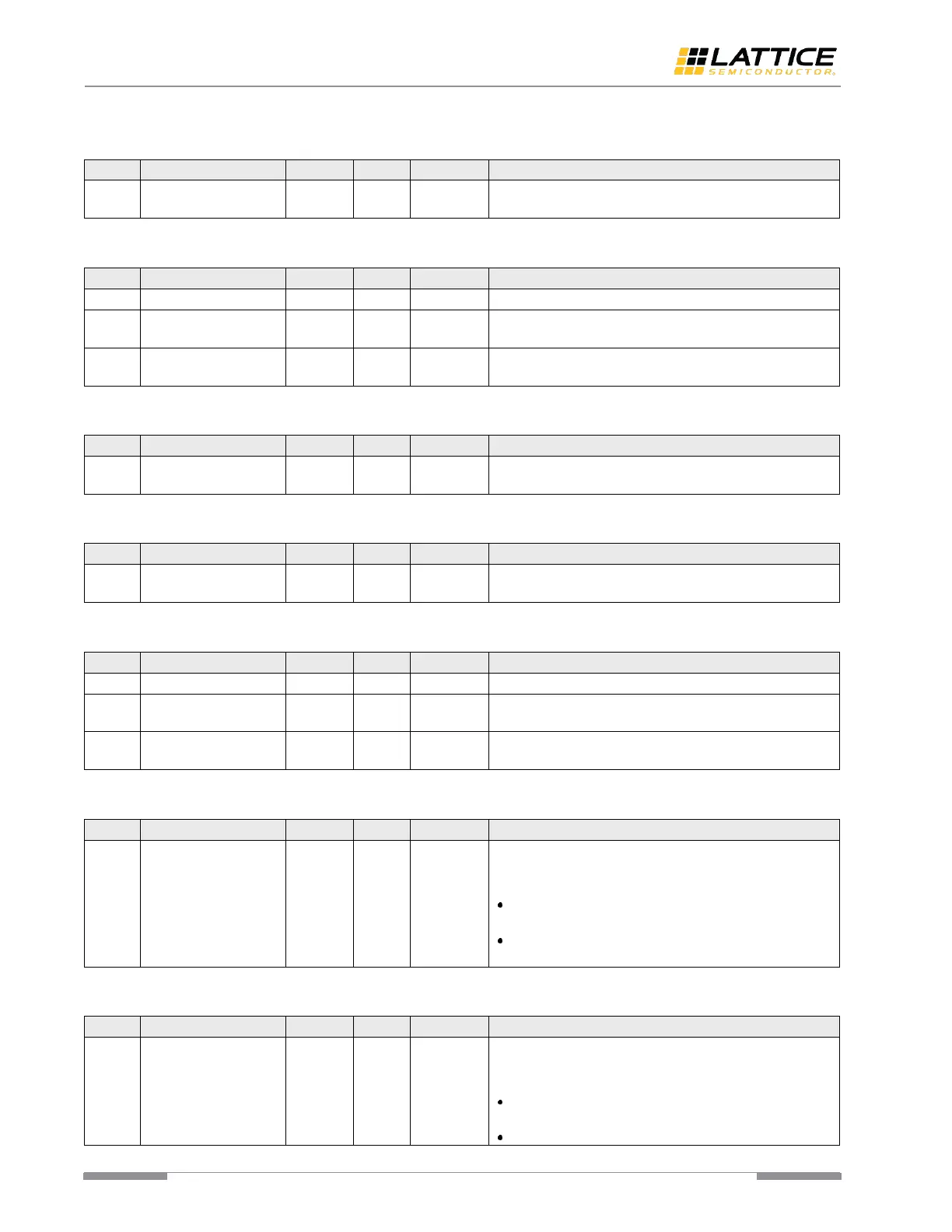

Table A. 39. Primary Word Alignment Pattern Byte 1 [reg32]

Specifies the 20-bit primary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Table A. 40. Primary Word Alignment Pattern MSB [reg33]

Specifies the 20-bit primary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Specifies the 20-bit primary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Table A. 41. Secondary Word Alignment Pattern Byte 0 [reg34]

Specifies the 20-bit secondary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Table A. 42. Secondary Word Alignment Pattern Byte 1 [reg35]

Specifies the 20-bit secondary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Table A. 43. Secondary Word Alignment Pattern MSB [reg36]

Specifies the 20-bit secondary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Specifies the 20-bit secondary word alignment pattern. In

10-bit width mode, only bits 9 to 0 are applied.

Table A. 44. Word Alignment Pattern Mask Code Byte 0 [reg37]

Word Align Mask Mode. Specifies the 20-bit word

alignment pattern. In 10-bit width mode, only bits 9 to 0

are applied.

1’b1 – the corresponding bit of word alignment pattern

is ignored during alignment pattern matching.

1’b0 – the corresponding bit of word alignment pattern

is not ignored during alignment pattern matching.

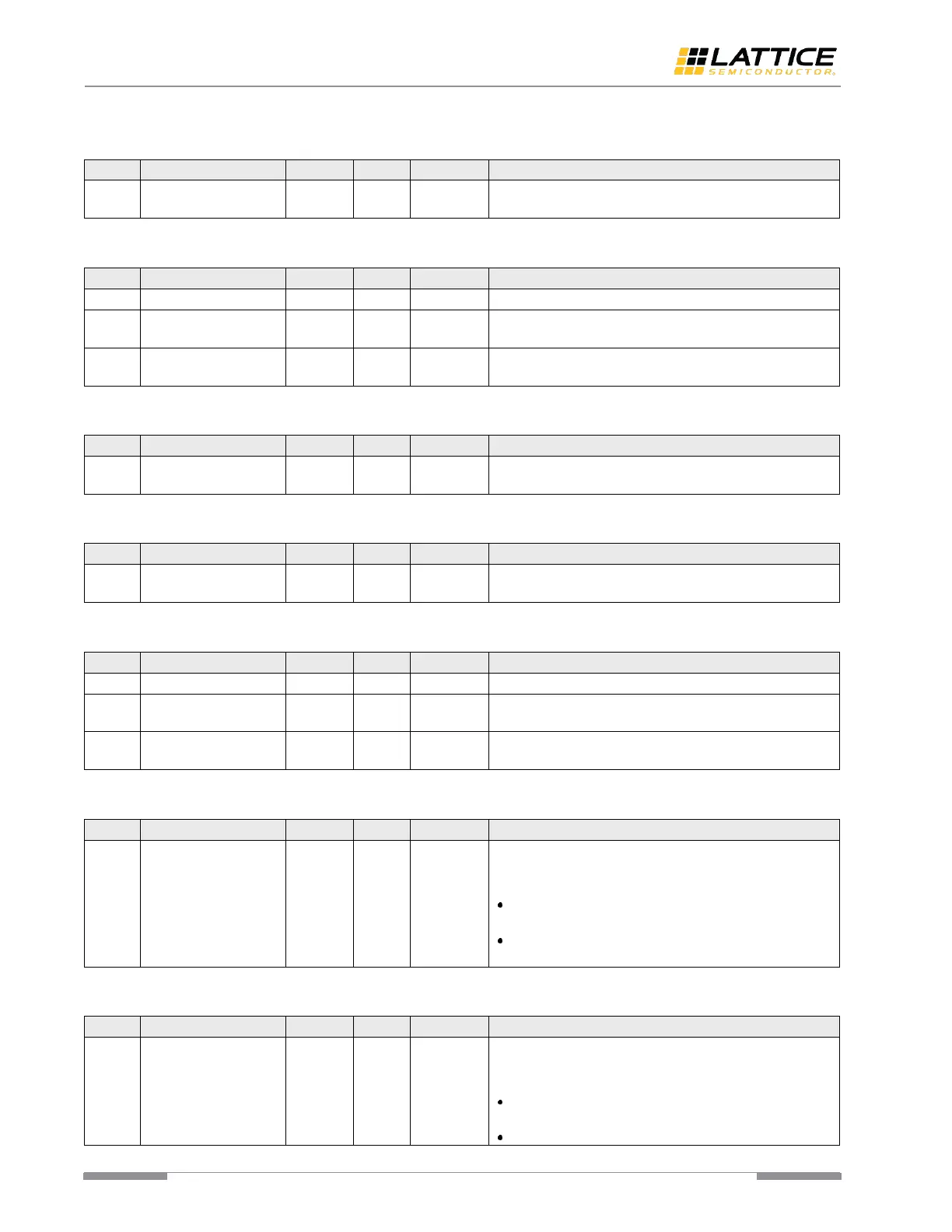

Table A. 45. Word Alignment Pattern Mask Code Byte 1 [reg38]

Word Align Mask Mode. Specifies the 20-bit word

alignment pattern. In 10-bit width mode, only bits 9 to 0

are applied.

1’b1 – the corresponding bit of word alignment pattern

is ignored during alignment pattern matching.

1’b0 – the corresponding bit of word alignment pattern

Loading...

Loading...