CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 83

All rights reserved. CONFIDENTIAL

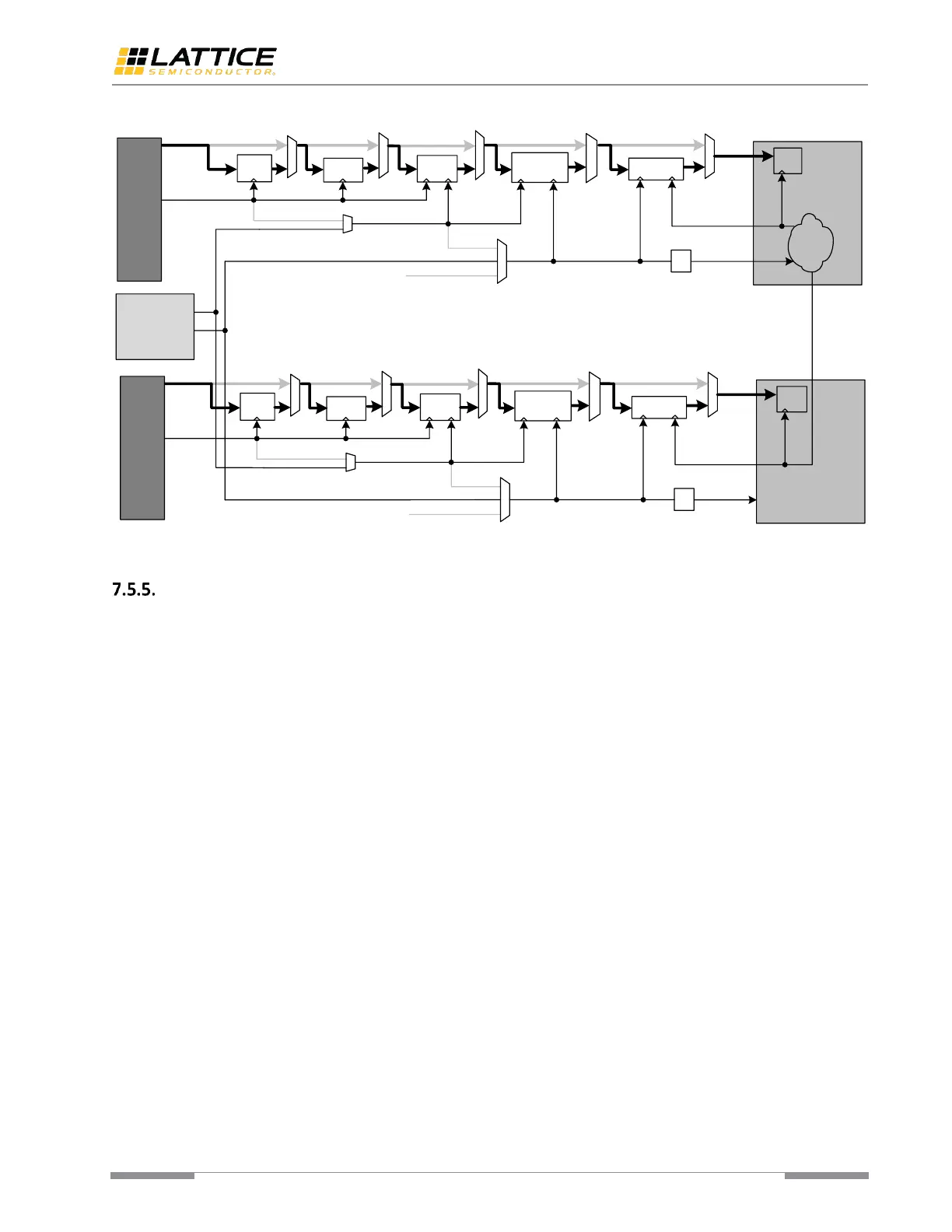

Figure 7.14. Case IV-b Clock Structure

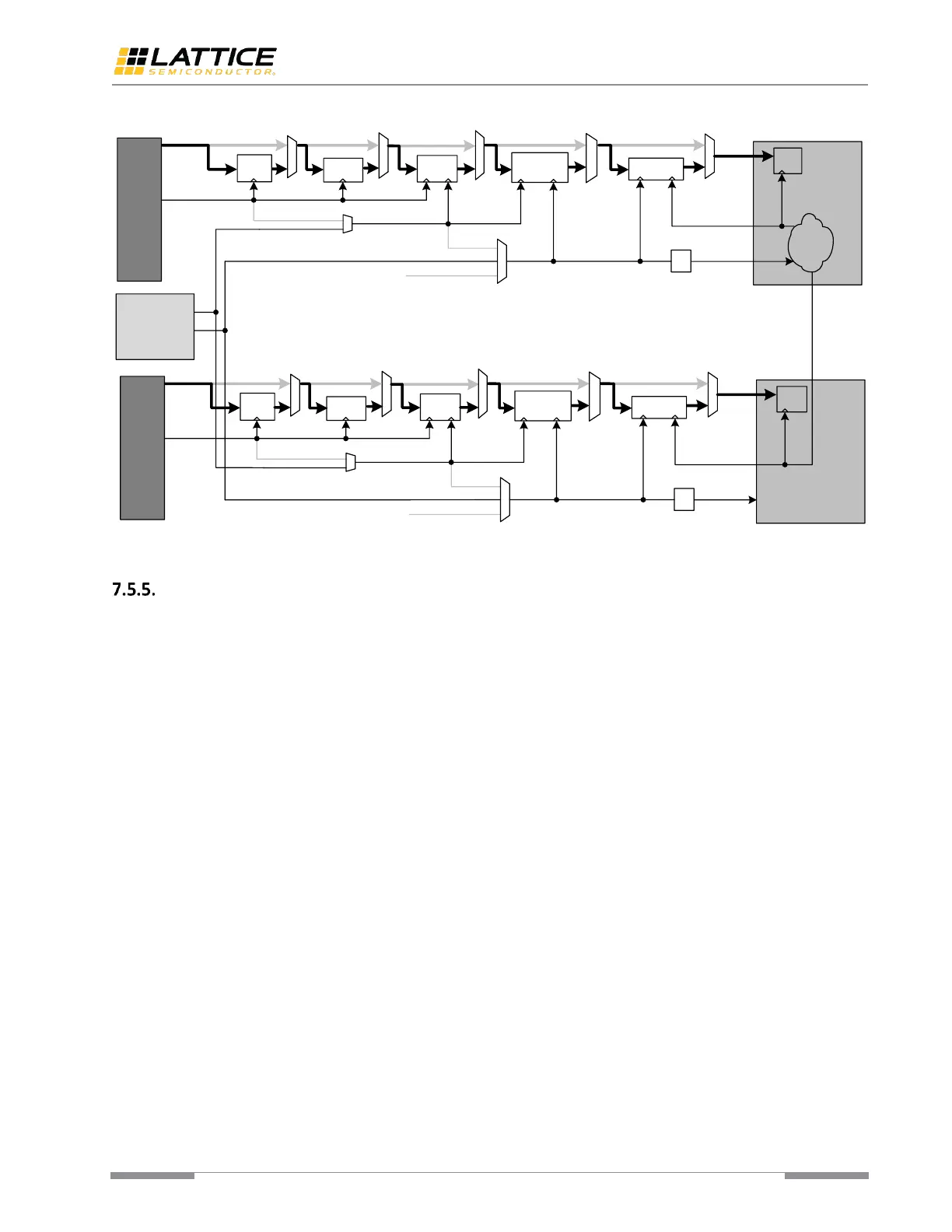

64B/66B PCS with GPLL

Case V-a: 64B/66B PCS with GPLL

As shown in Figure 7.15, the tx_pcs_clk is generated clock from PMA Tx PLL, and the rx_pcs_clk is recovered clock from

PMA Rx CDR. The source of tx_out_clk and rx_out_clk can be divided-by-two version or divided-by-four of tx_pcs_clk

and rx_pcs_clk respectively.

A General PLL (GPLL) is recommended to be used in fabric to generate the 156.25 MHz clock to drive both Tx XGMII

data path and Rx XGMII data path.

All modules inside 64B/66B PCS channel are recommended to be enabled, considering this 64B/66B PCS being designed

for Ethernet 10GBASE-R only. However, certain module can be disabled or bypassed only for test purposes.

Figure 7.15 shows an example of all modules being enabled. The tx_out_clk is used to drive GPLL to generate

156.25MHz tx_usr_clk and rx_usr_clk. Tx FIFO is enabled to eliminate the clock frequency difference between

tx_pcs_divclk and tx_usr_clk. Rx FIFO is enabled to eliminate the clock frequency difference between rx_pcs_divclk and

rx_usr_clk. Check Tx FIFO section for the Tx FIFO write timing diagram, and the Rx FIFO section for the Rx FIFO read

timing diagram.

The Rx FIFO also works as CTC FIFO, to implements the clock tolerance compensation required by Ethernet 10GBASE-R

protocol.

Loading...

Loading...