CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

132 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

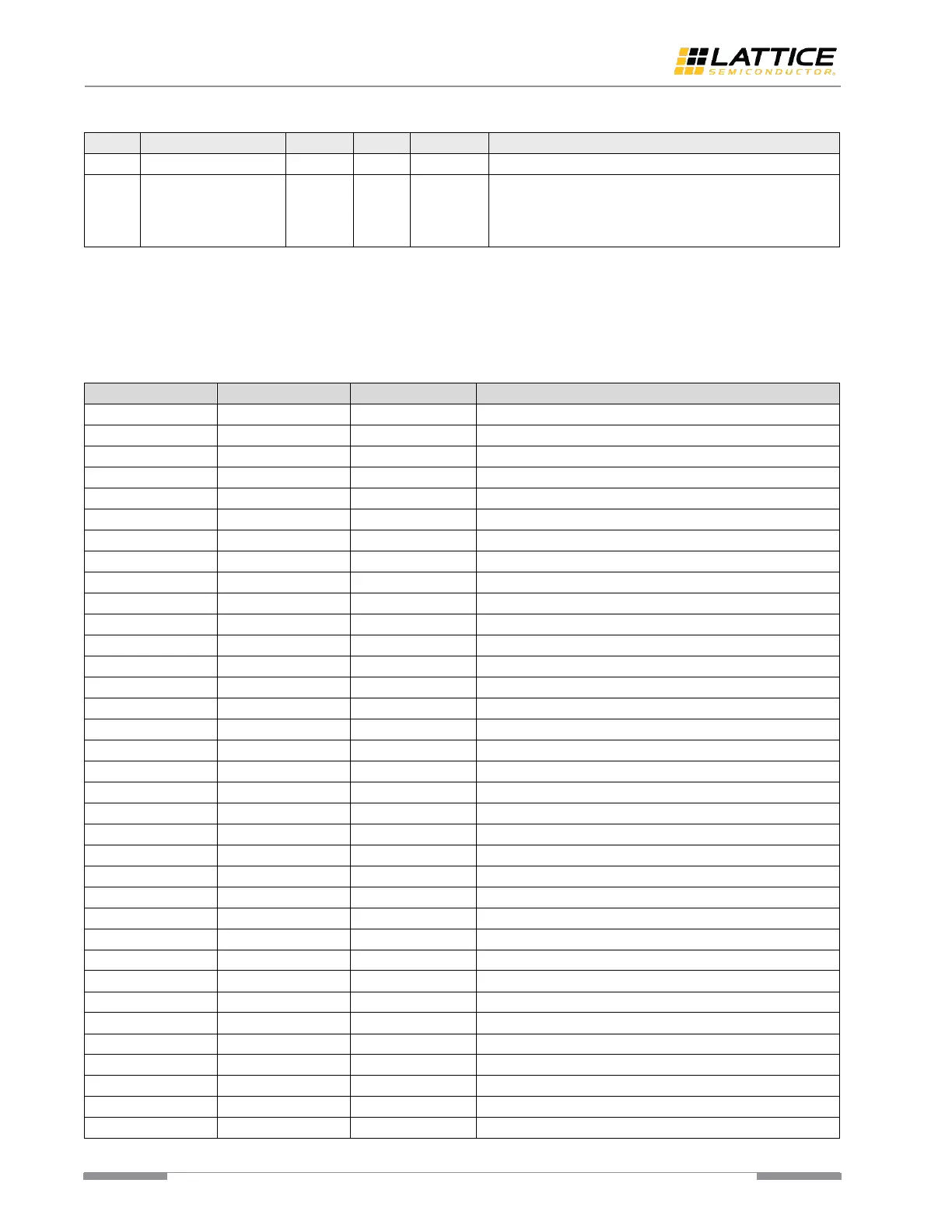

Table A. 29. Update Settings Command Register [reg80]

This bit is transient (read always report 0) where writing

1’b1 to this bit will trigger a new computation of PMA

settings based on values written into related PMA

registers.

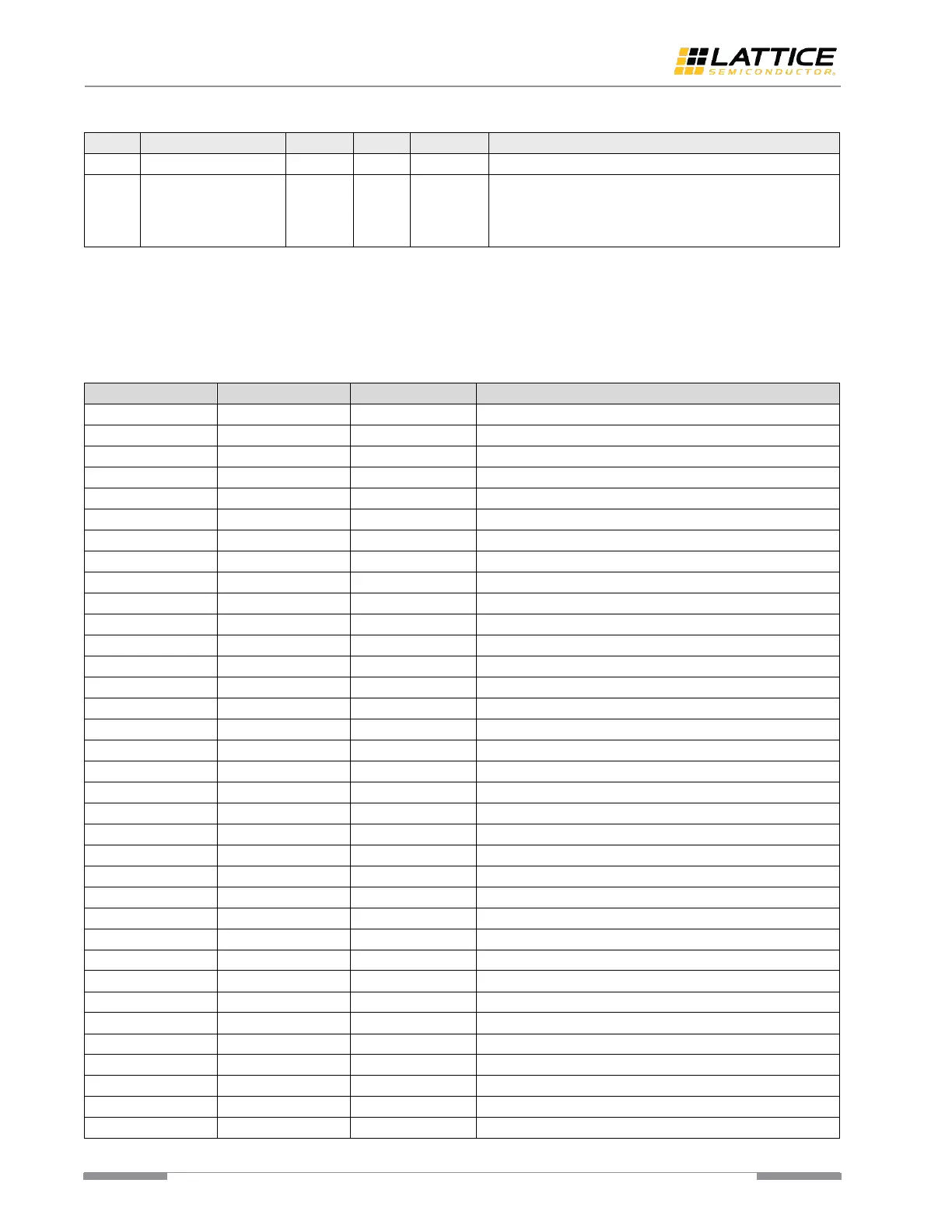

A.2. MPCS Registers

A.2.1. Register Address

Table A. 30. Register Address

MPCS Data Path Selection.

Primary Word Alignment Pattern Byte 0.

Primary Word Alignment Pattern Byte 1.

Primary Word Alignment Pattern MSB.

Secondary Word Alignment Pattern Byte 0.

Secondary Word Alignment Patter Byte 1.

Secondary Word Alignment Pattern MSB.

Word Alignment Pattern Mask Code Byte 0.

Word Alignment Pattern Mask Code Byte 1.

Word Alignment Pattern Mask Code MSB.

Sync_Det FSM Configuration 0.

Sync_Det FSM Configuration 1.

Sync_Det FSM Configuration 2.

Sync_Det FSM Configuration 3.

Number of Bit Slipped During Word Alignment.

Primary Sync_Det Pattern Byte 0.

Primary Sync_Det Pattern Byte 1.

Primary Sync_Det Pattern Byte 2.

Primary Sync_Det Pattern Byte 3.

Primary Sync_Det Pattern MSB.

Secondary Sync_Det Pattern Byte 0.

Secondary Sync_Det Pattern Byte 1.

Secondary Sync_Det Pattern Byte 2.

Secondary Sync_Det Pattern Byte 3.

Secondary Sync_Det Pattern MSB.

Sync_Det Pattern Mask Code Byte 0.

Sync_Det Pattern Mask Code Byte 1.

Sync_Det Pattern Mask Code Byte 2.

Sync_Det Pattern Mask Code Byte 3.

Loading...

Loading...