CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

22 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

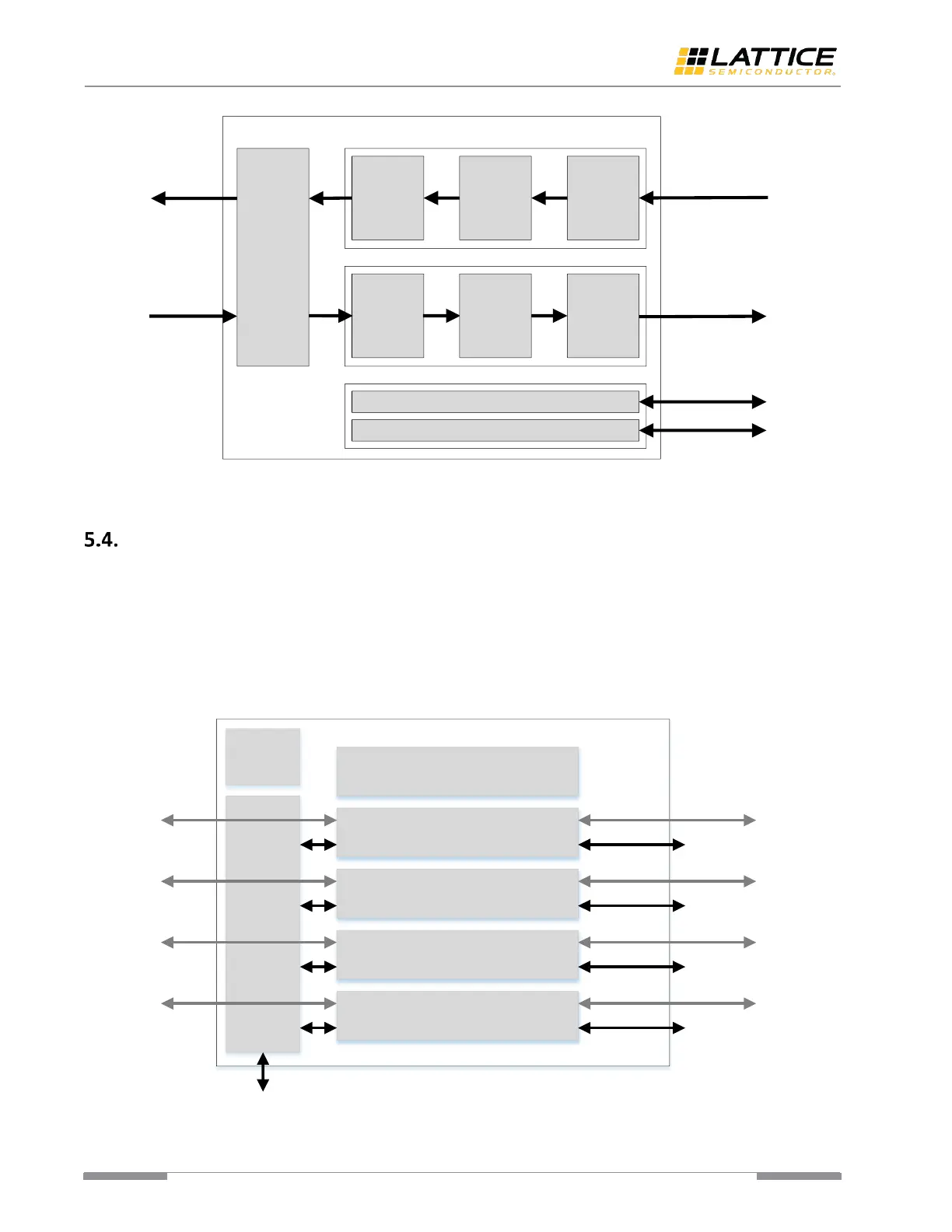

PCI Express Link Layer Core

Rx

PHY

Layer

CLK, Configuration, and Management

Configuration Registers

PHY TX

PHY RX

VC0_TX

VC0_RX

Power Management

Error Reporting (AER)

LMMI

PHY

Interface

(PIPE)

Tx

PHY

Layer

Tx

Data

Link

Layer

Tx

Trans

Layer

Rx

Data

Link

Layer

Rx

Trans

Layer

Figure 5.4. PCI Express Link Layer Functional Diagram

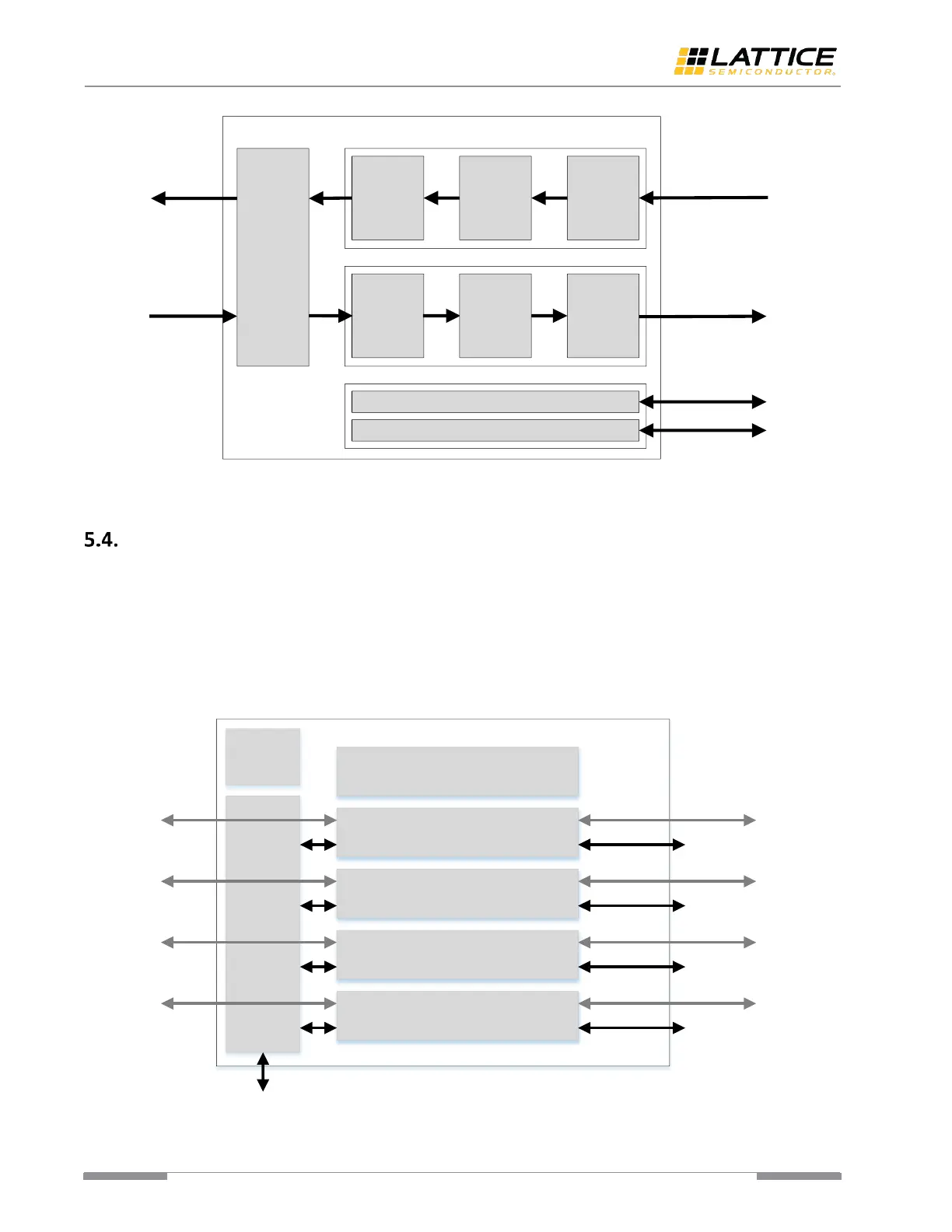

MPCS Architecture

CertusPro-NX Multi-Protocol PCS is designed for popular serial protocols other than PCI Express, such as Ethernet

SGMII, XAUI, QSGMII, 10GBASE-R, SLVS-EC, CoaXpress, and DP/eDP. MPCS can be configured as Generic 8B/10B mode,

for user-defined serial protocols other than those listed in the Features section.

Each MPCS Quad includes four channels. One Quad Common block communicates with each channel within the Quad

to implement the multiple lane alignment function for both transmitter and receiver. The Quad Common block also

talks to neighboring Quads to implement the lane alignment across Quad boundary. Figure 5.5 shows the simplified

block diagram of MPCS Quad.

Loading...

Loading...