CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 135

All rights reserved. CONFIDENTIAL

selected source/interface for the Tx Path.

1’b1 – use rx_pcsmode_sel to override the MODESEL to

set the MPCS mode for the Tx path.

1’b0 – use the MODESEL to set the MPCS mode for the

Tx path.

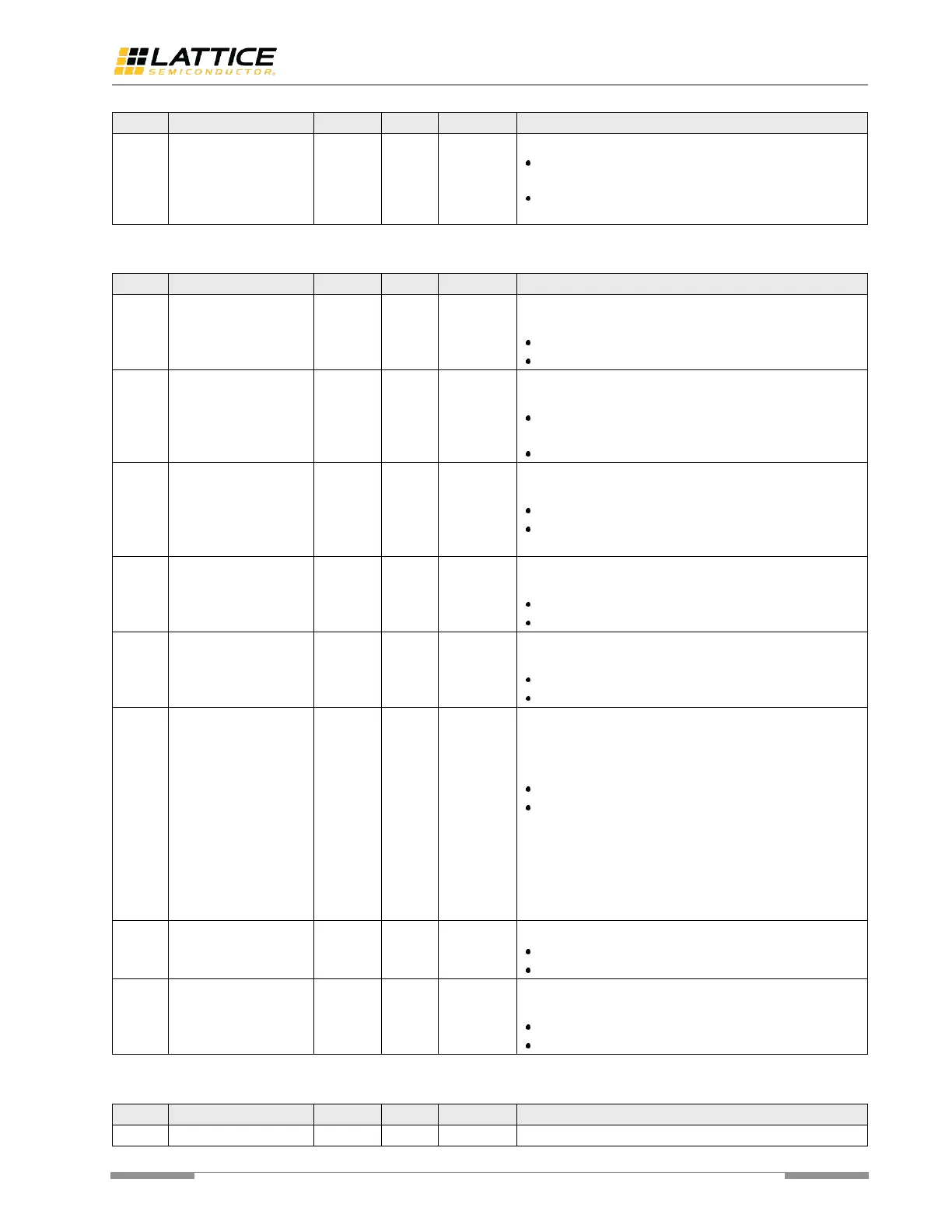

Table A. 32. Tx Path Control [reg10]

Phase Matching FIFO. Specifies the Phase Matching FIFO is

enabled or disabled (Tx lane-to-lane Deskew).

1’b1 – Phase Matching FIFO disabled.

1’b0 – Phase Matching FIFO enabled.

Bond Mask. The banded channel mode is defined by

mc1_tx_bond_mode signal.

1’b1 – exclude this channel from bonded channel

group.

1’b0 – do not exclude this channel.

Bus Width. Specifies the internal data bus width for Tx

Path.

1’b1 – internal data bus is 20-bit width.

1’b0 – internal data bus is 10-bit width.

Note: this bit is not applicable for 64B/66B PCS mode.

8B/10B Encoding Enable. Specifies the 8B/10B encoding is

enabled or disabled.

1’b1 – Encoding disabled.

1’b0 – Encoding enabled.

Tx FIFO Enable. Specifies the Tx phase compensation FIFO

is enabled or disabled.

1’b1 – Tx phase compensation FIFO disabled.

1’b0 – Tx phase compensation FIFO enabled.

Gearing Enable. Specifies the 2:1 Gearing is enabled or

disabled. This bit controls the 8B/10B path and PMA Only

path gearing logic, as well as the “tx_out_clk” for all PCS

modes.

1’b1 – Gearing is enabled.

1’b0 – Gearing is disabled.

Note: In 8B/10B PCS mode and PMA Only mode, the

output clock (tx_out_clk) is driven by the divided-by-two

clock, if this bit is set to “1”. In 64B/66B PCS mode, the

output clock (tx_out_clk) is driven by the clock with

doubled rate of default output clock, if this bit is set to

“1”.

Soft resets the Tx Path not including the register space.

1’b1 – reset the Tx MPCS path.

1’b0 – do not reset the Tx MPCS path.

TX Path Enable. Specifies the MPCS channel Tx Path is

enabled or disabled.

1’b1 – MPCS channel Tx Path is disabled.

1’b0 – MPCS channel Tx Path is enabled.

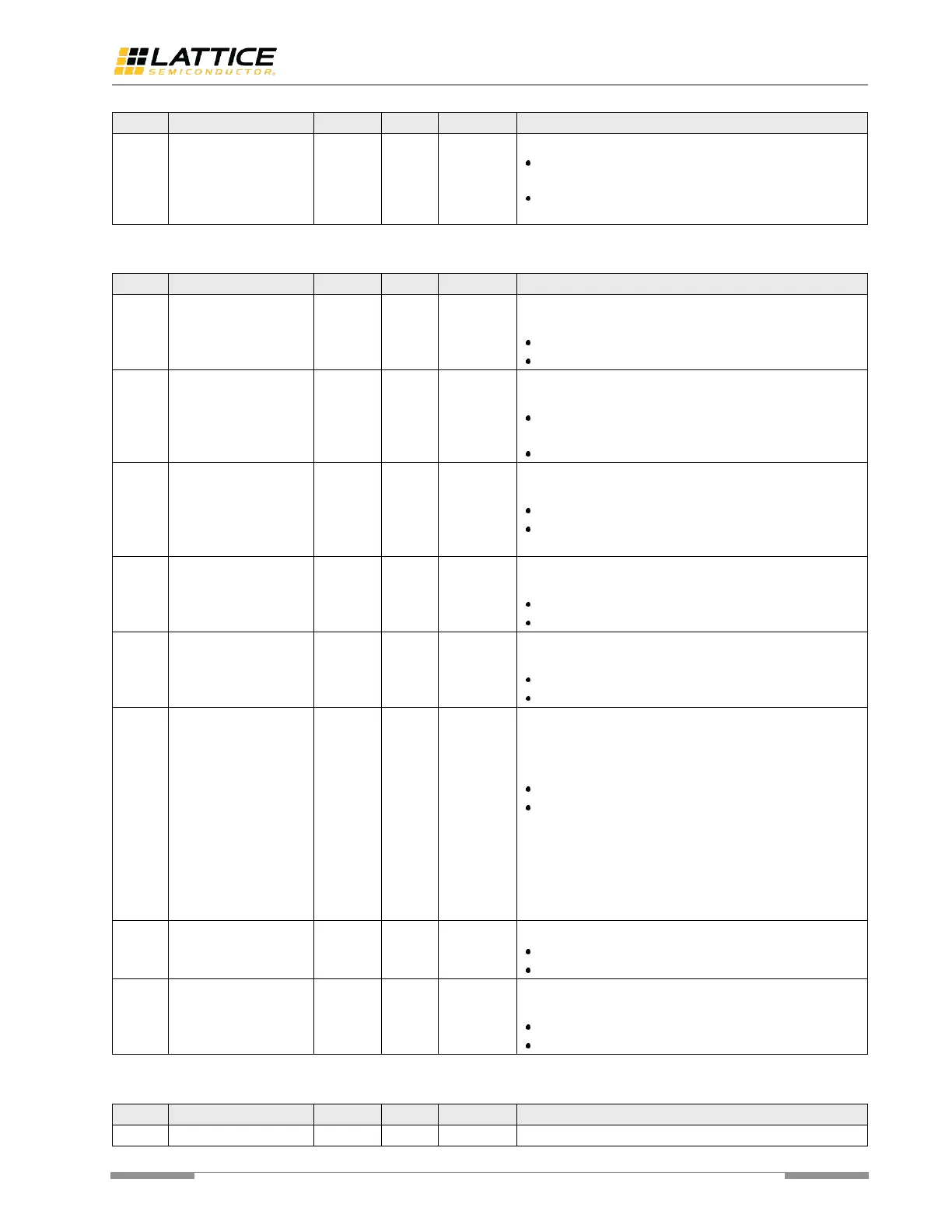

Table A. 33. 8B/10B Encoder Control [reg11]

Loading...

Loading...