CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

148 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

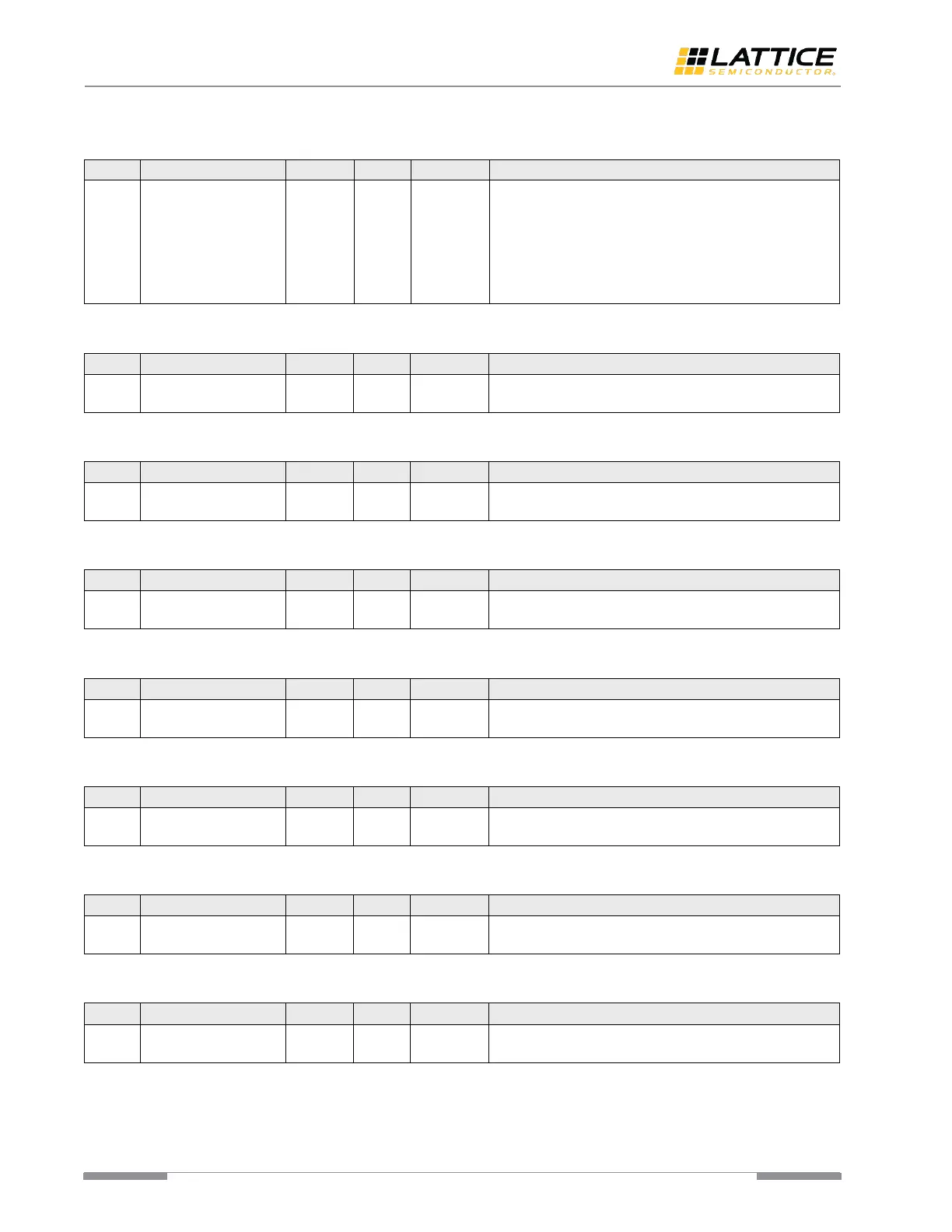

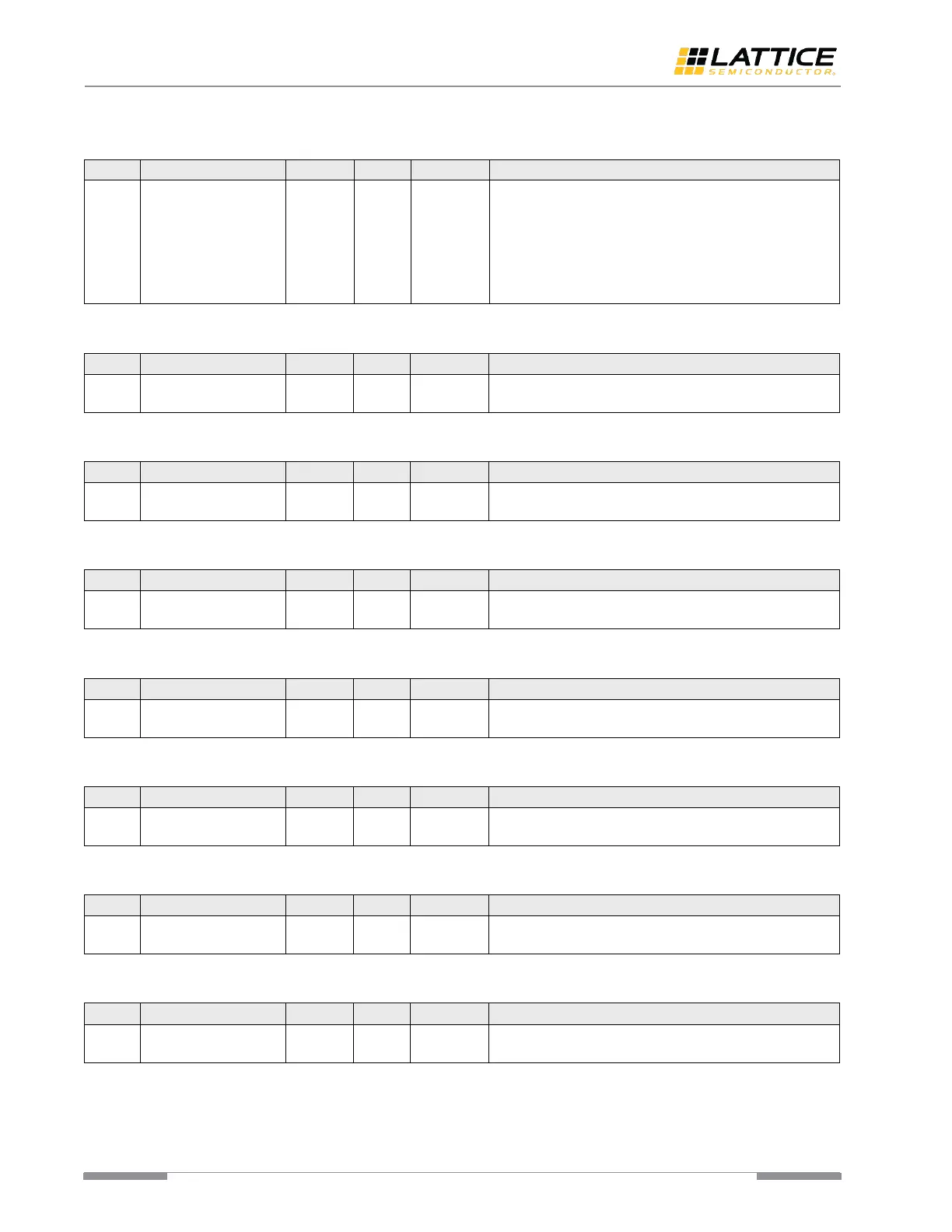

Table A. 103. 10GBASE-R Block Error Counter [reg91]

10GBASE-R Block Error Counter register reflects the

errored blocks counter is an eight-bit count defined by the

errored_block_count counter specified in 49.2.14.2 for

10GBASE-R. These bits are to be reset to all zeros when

the errored blocks count is read or upon execution of the

PCS reset. These bits are to be held at all ones in the case

of overflow.

Table A. 104. 10GBASE-R Test Pattern Seed A Byte 0 [reg92]

This register defines byte 0 of 10GBASE-R PCS test pattern

seed A.

Table A. 105. 10GBASE-R Test Pattern Seed A Byte 1 [reg93]

This register defines byte 1 of 10GBASE-R PCS test pattern

seed A.

Table A. 106. 10GBASE-R Test Pattern Seed A Byte 2 [reg94]

This register defines byte 2 of 10GBASE-R PCS test pattern

seed A.

Table A. 107. 10GBASE-R Test Pattern Seed A Byte 3 [reg95]

This register defines byte 3 of 10GBASE-R PCS test pattern

seed A.

Table A. 108. 10GBASE-R Test Pattern Seed A Byte 4 [reg96]

This register defines byte 4 of 10GBASE-R PCS test pattern

seed A.

Table A. 109. 10GBASE-R Test Pattern Seed A Byte 5 [reg97]

This register defines byte 5 of 10GBASE-R PCS test pattern

seed A.

Table A. 110. 10GBASE-R Test Pattern Seed A Byte 6 [reg98]

This register defines byte 6 of 10GBASE-R PCS test pattern

seed A.

Loading...

Loading...