CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 147

All rights reserved. CONFIDENTIAL

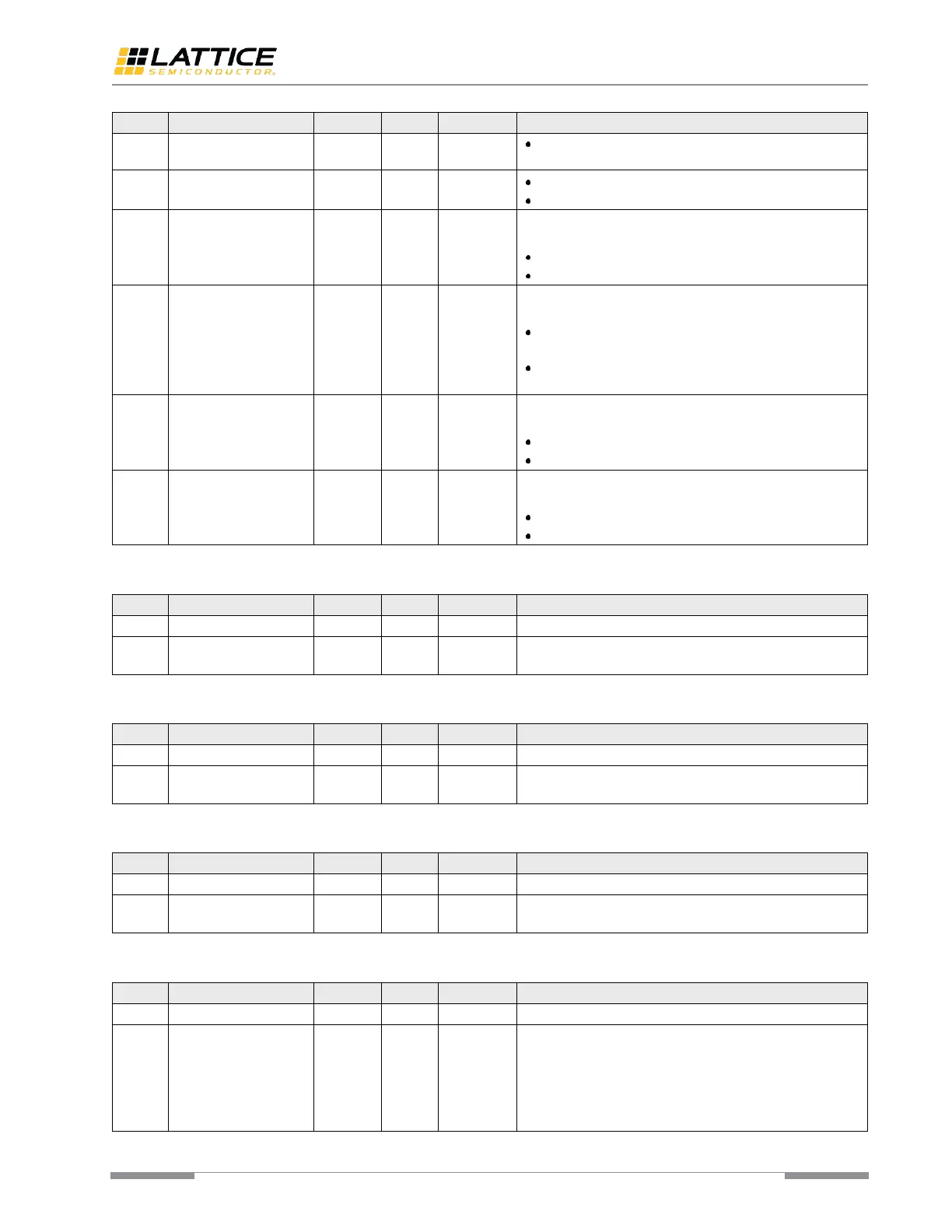

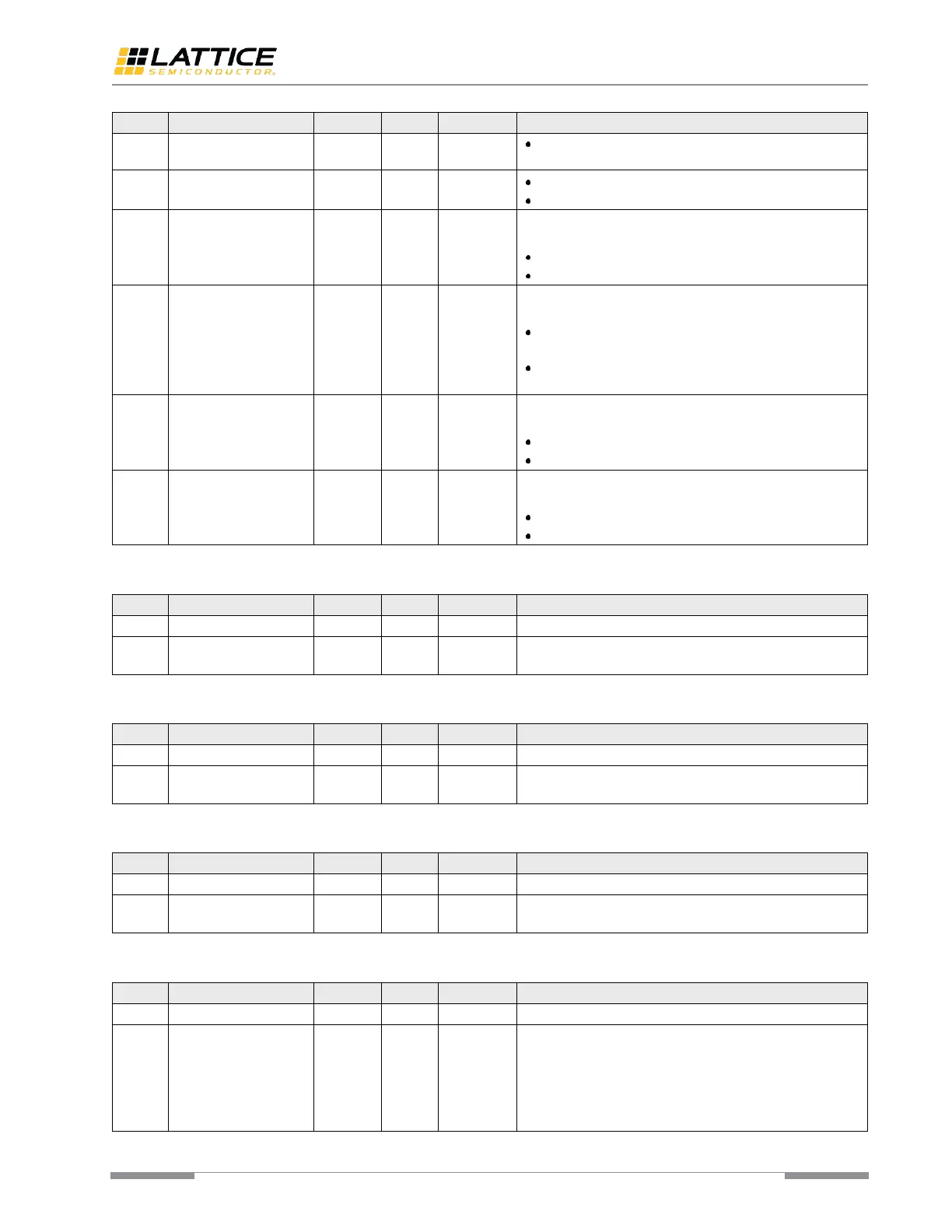

1’b0 – Only delete one sequence ordered set each time

when doing clock frequency compensation.

1’b1 – No GPLL is used to generate user clock.

1’b0 – GPLL is used to generate user clock.

Enable 64B/66B Block Aligner. Specifies the 64B/66B block

aligner is enabled or disabled.

1’b1 – 64B/66B block aligner is disabled.

1’b0 – 64B/66B block aligner is enabled.

Enable 64B/66B CTC. Specifies the 64B/66B Clock

Frequency Compensation is enabled or disabled.

1’b1 – 64B/66B Clock Frequency Compensation is

disabled.

1’b0 – 64B/66B Clock Frequency Compensation is

enabled.

Enable 64B/66B Decoder. Specifies the 64B/66B Decoder

is enabled or disabled.

1’b1 – 64B/66B Decoder is disabled.

1’b0 – 64B/66B Decoder is enabled.

Enable 64B/66B Descrambler. Specifies the 64B/66B

Descrambler is enabled or disabled.

1’b1 – 64B/66B Descrambler is disabled.

1’b0 – 64B/66B Descrambler is enabled.

Table A. 99. 64B/66B PCS CTC High Water Line Control [reg84]

64B/66B PCS CTC High water line reflects the high water

line of clock frequency compensation.

Table A. 100. 64B/66B PCS CTC Low Water Line Control [reg85]

64B/66B PCS CTC Low water line reflects the low water

line of clock frequency compensation.

Table A. 101. 64B/66B PCS Block Align Shift [reg86]

64B/66B PCS Block Align Shift register reflects the bit

shifting of block alignment.

Table A. 102. 10GBASE-R BER Counter [reg90]

10GBASE-R BER Counter register reflects the BER counter

is a six-bit-count as defined by the ber_count variable in

49.2.14.2 for 10GBASE-R. These bits are the reset to all

zeros when the register is read or upon execution of the

PCS reset. These bits are to be held at all ones in the case

of overflow.

Loading...

Loading...