CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

20 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

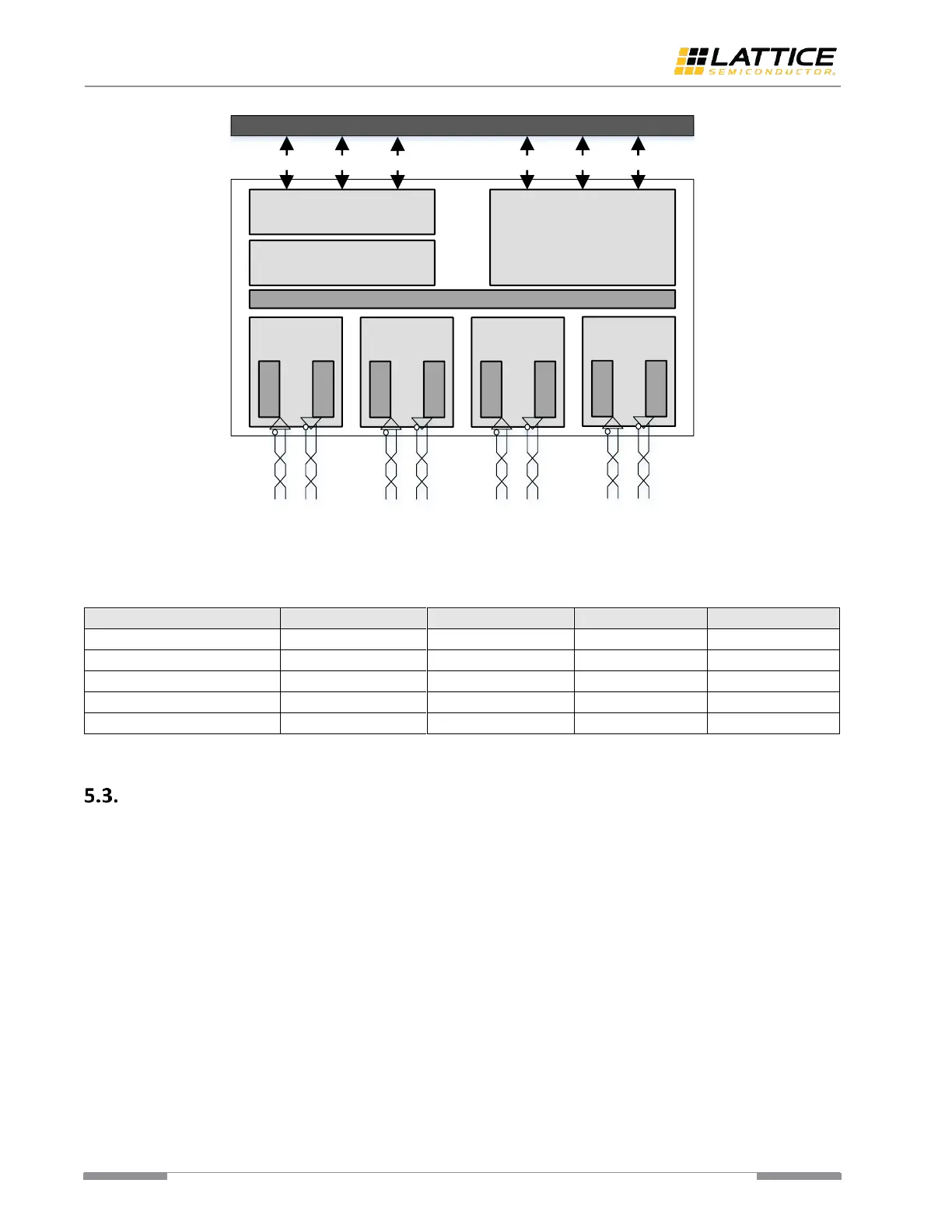

Figure 5.2. CertusPro-NX SerDes/PCS Quad Architecture

Table 5.3 shows the specific block usage for the corresponding SerDes/PCS mode.

Table 5.3. Block Usage for the Corresponding SerDes/PCS Mode

PCI Express Architecture

The CertusPro-NX PCI Express Link Layer block is a hard IP, which supports PCI Express Gen1, Gen2, and Gen3, and is

compatible with PCI-SIG PCI Express Base Spec version 3.1a. The PCI Express Link Layer Block implements PHY Layer

adaption, Data Link Layer, and Transaction Layer. The PCI Express Link Layer block together with PCI Express PCS, PMA

Controller and PMA, constitute the complete PCI Express Hard IP block.

The PCI Express Hard IP supports both Endpoint and Root Complex modes. It supports up to four physical functions.

Each of the four functions has independent PCI Express configurations space. It also supports ECC and parity data path

protection. You can configure this IP as PIPE mode, which is compliant to industry PIPE standard version 4.4, by

bypassing Link Layer block. The LMMI interface is provided in the top wrapper that is to be used in user-controlled IP

core configuration.

The PCI Express Link Layer Quad for all CertusPro-NX devices has four PIPE interfaces that can be used in different

number of links. This can provide the maximum flexibility, depending on the bandwidth of the application

requirements.

Figure 5.3 shows the architecture of the CertusPro-NX PCI Express Hard IP. There are four physical functions in the Link

Layer ×4 block. There are four physical functions in the Link Layer ×1 block. Total there are eight physical functions in

one Link Layer Quad. PCI Express Configuration Space access and Error Reporting are done through the dedicated

interface (PCI Express Configuration Register Interface, UCFG). The core Configuration and Status Registers can be

accessed using the corresponding LMMI interface per Link Layer block. PCI Express Link Layer block interface to PCI

Loading...

Loading...