CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 131

All rights reserved. CONFIDENTIAL

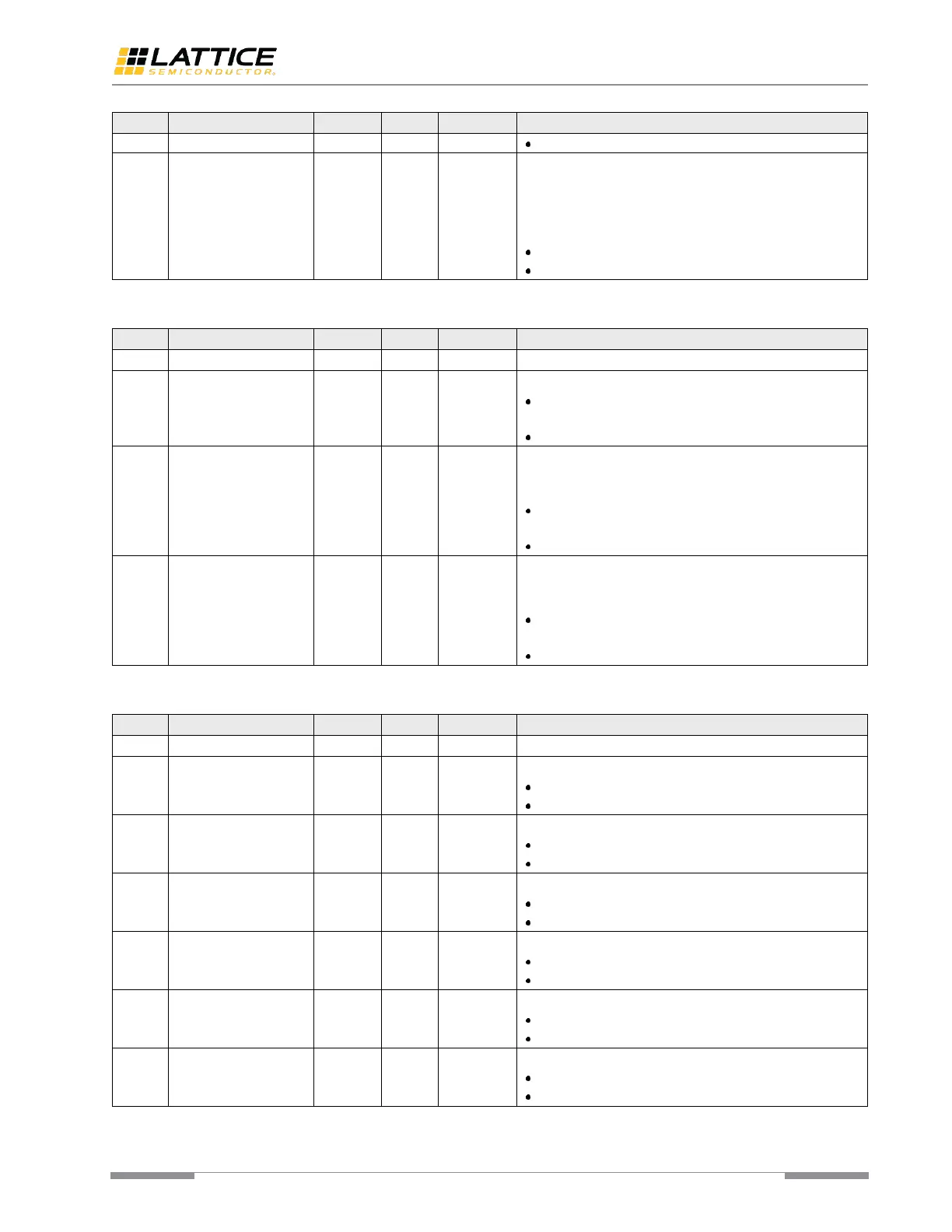

Enables the plesiochronous loopback mode which forces

the PCS to loopback data from Rx back to Tx after the PCIe

elastic buffer function. It is equivalent to PCIe slave

loopback except that it is forced by a register instead of

controlled by the PCIe MAC layer.

1’b1 – enabling the plesiochronous loopback mode.

1’b0 – normal operation.

Table A. 27. CDR PLL Manual Control [reg79]

Forces the CDR PLL state machine to fine grain state.

1’b1 – forces the CDR PLL state machine to fine grain

state.

1’b0 – normal operation.

Forces the CDR PLL state machine to coarse grain mode. In

this state, the CDR PLL performs a coarse grain lock on

received data enabling to adjust its clock up to 5000 ppm.

1’b1 – forces the CDR PLL state machine to coarse grain

state.

1’b0 – normal operation.

Forces the CDR PLL state machine to frequency lock state.

In this state, the CDR PLL does not lock on received data

but on reference clock.

1’b1 – forces the CDR PLL state machine to frequency

lock state.

1’b0 – normal operation.

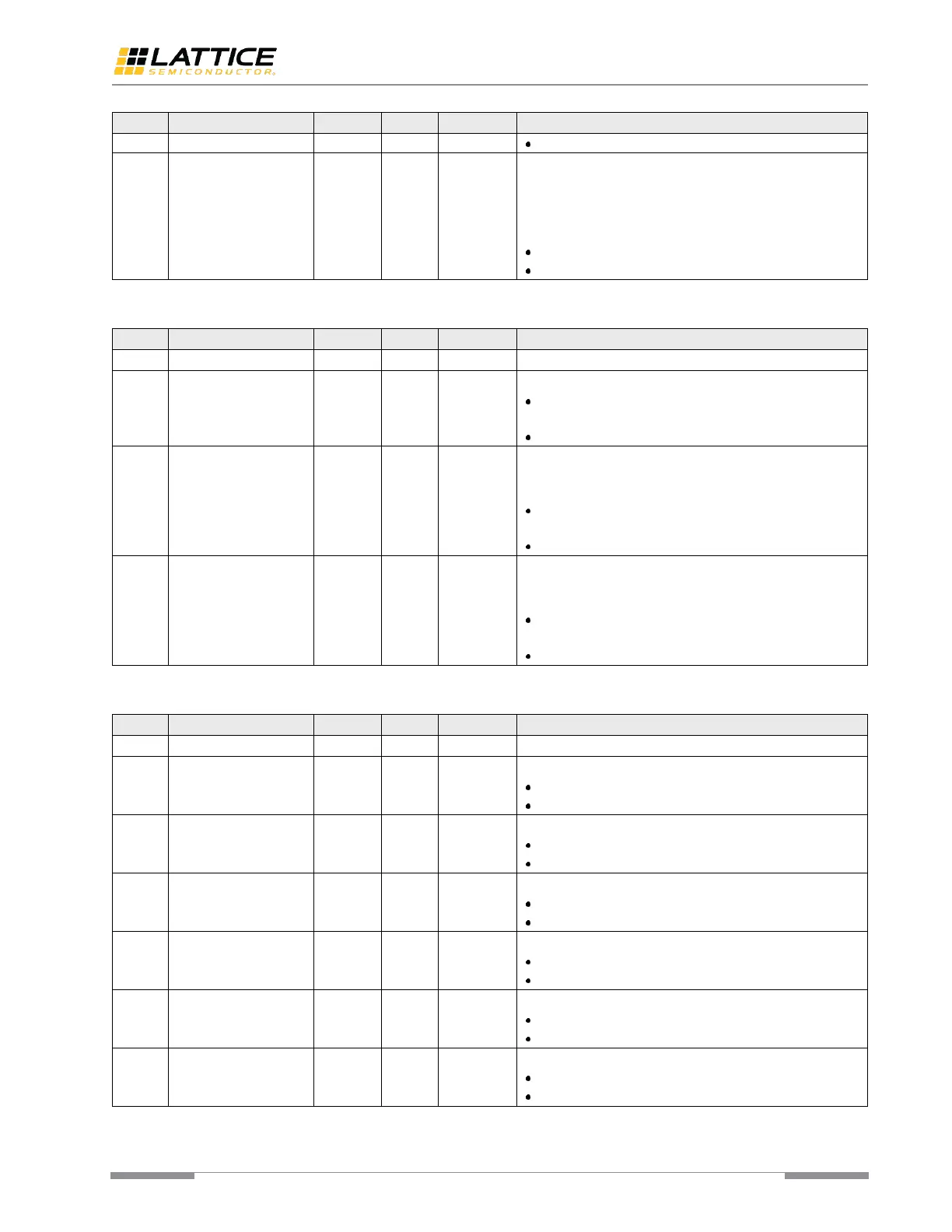

Table A. 28. PMA Status [reg7f]

CDR PLL status.

1’b1 – locked.

1’b0 – loss of lock.

Tx PLL status.

1’b1 – locked.

1’b0 – loss of lock.

CDR PLL lock status.

1’b1 – locked on Rx data.

1’b0 – not locked on Rx data.

Rx activity detection.

1’b1 – Rx activity detected.

1’b0 – loss of signal.

CDR PLL reset status.

1’b1 – CDR PLL is under reset.

1’b0 – reset is released.

Tx PLL reset status.

1’b1 – Tx PLL is under reset.

1’b0 – reset is released.

Loading...

Loading...