CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

FPGA-TN-02245-0.81 © 2020-2021 Lattice Semiconductor 141

All rights reserved. CONFIDENTIAL

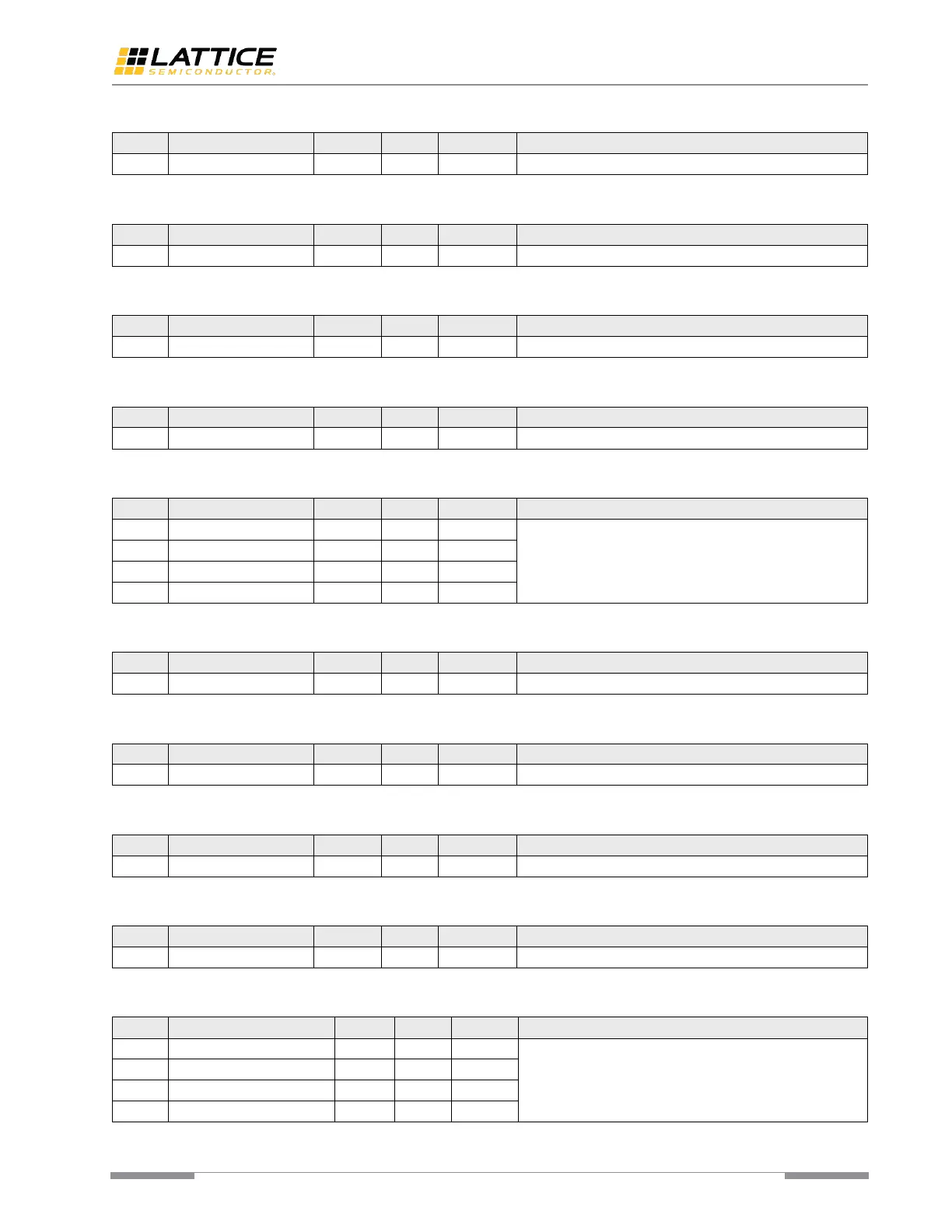

Table A. 57. Secondary Sync_Det Pattern Byte 0 [reg44]

Secondary Sync_Det Pattern Byte 0.

Table A. 58. Secondary Sync_Det Pattern Byte 1 [reg45]

Secondary Sync_Det Pattern Byte 1.

Table A. 59. Secondary Sync_Det Pattern Byte 2 [reg46]

Secondary Sync_Det Pattern Byte 2.

Table A. 60. Secondary Sync_Det Pattern Byte 3 [reg47]

Secondary Sync_Det Pattern Byte 3.

Table A. 61. Secondary Sync_Det Pattern Byte MSB [reg48]

Secondary Sync_Det Pattern MSB Register reflects the bits

9 to 8 of secondary Sync_Det pattern byte 3 to 0.

Table A. 62. Sync_Det Pattern Mask Code Byte 0 [reg49]

Sync_Det Pattern Mask Code Byte 0.

Table A. 63. Sync_Det Pattern Mask Code Byte 1 [reg4a]

Sync_Det Pattern Mask Code Byte 1.

Table A. 64. Sync_Det Pattern Mask Code Byte 2 [reg4b]

Sync_Det Pattern Mask Code Byte 2.

Table A. 65. Sync_Det Pattern Mask Code Byte 3 [reg4c]

Sync_Det Pattern Mask Code Byte 3.

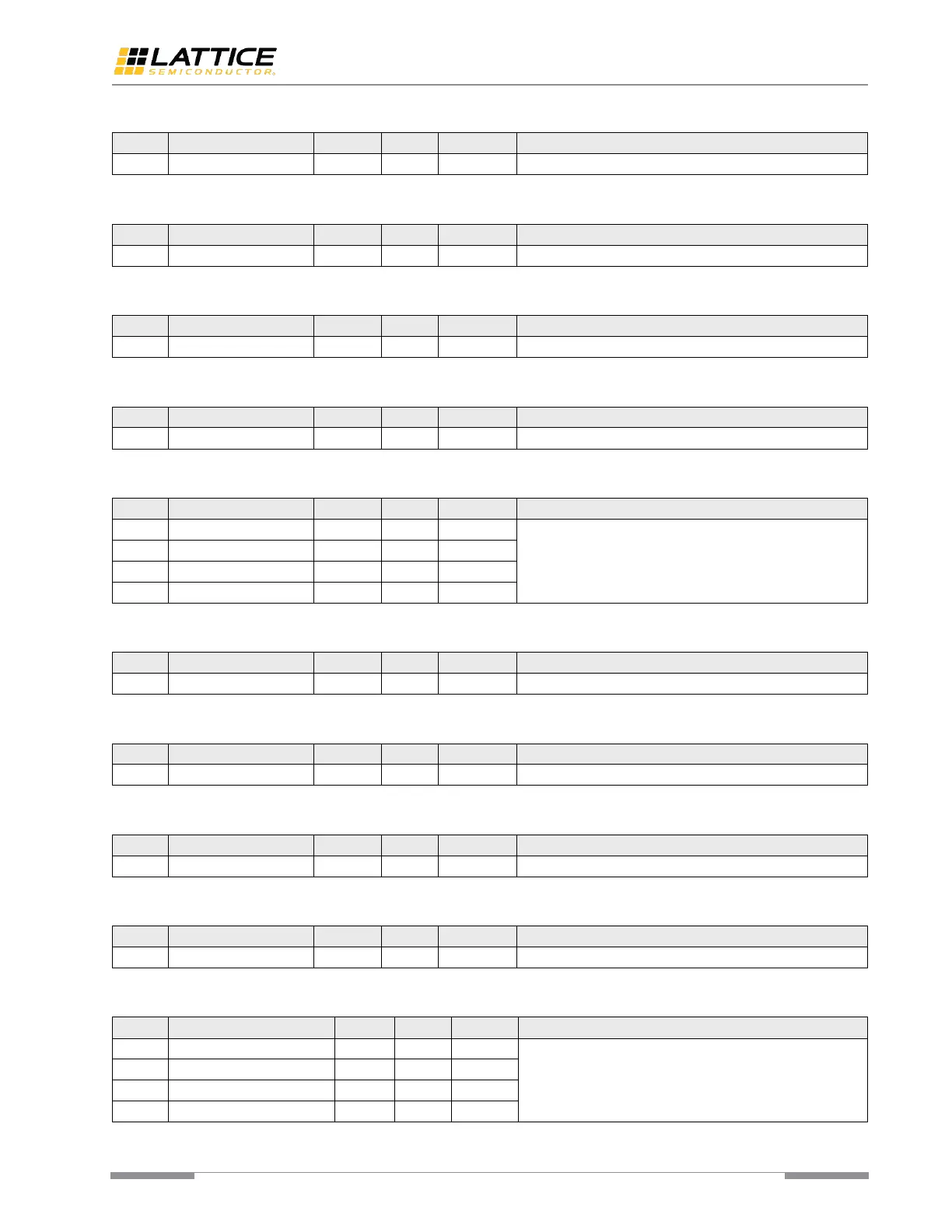

Table A. 66. Sync_Det Pattern Mask Code MSB [reg4d]

Sync_Det Pattern Mask Code MSB Register reflects the

bits 9 to 8 of Sync_Det pattern mask code byte 3 to 0.

Loading...

Loading...