CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

130 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

Note: This register can be reprogrammed when the PHY is under reset.

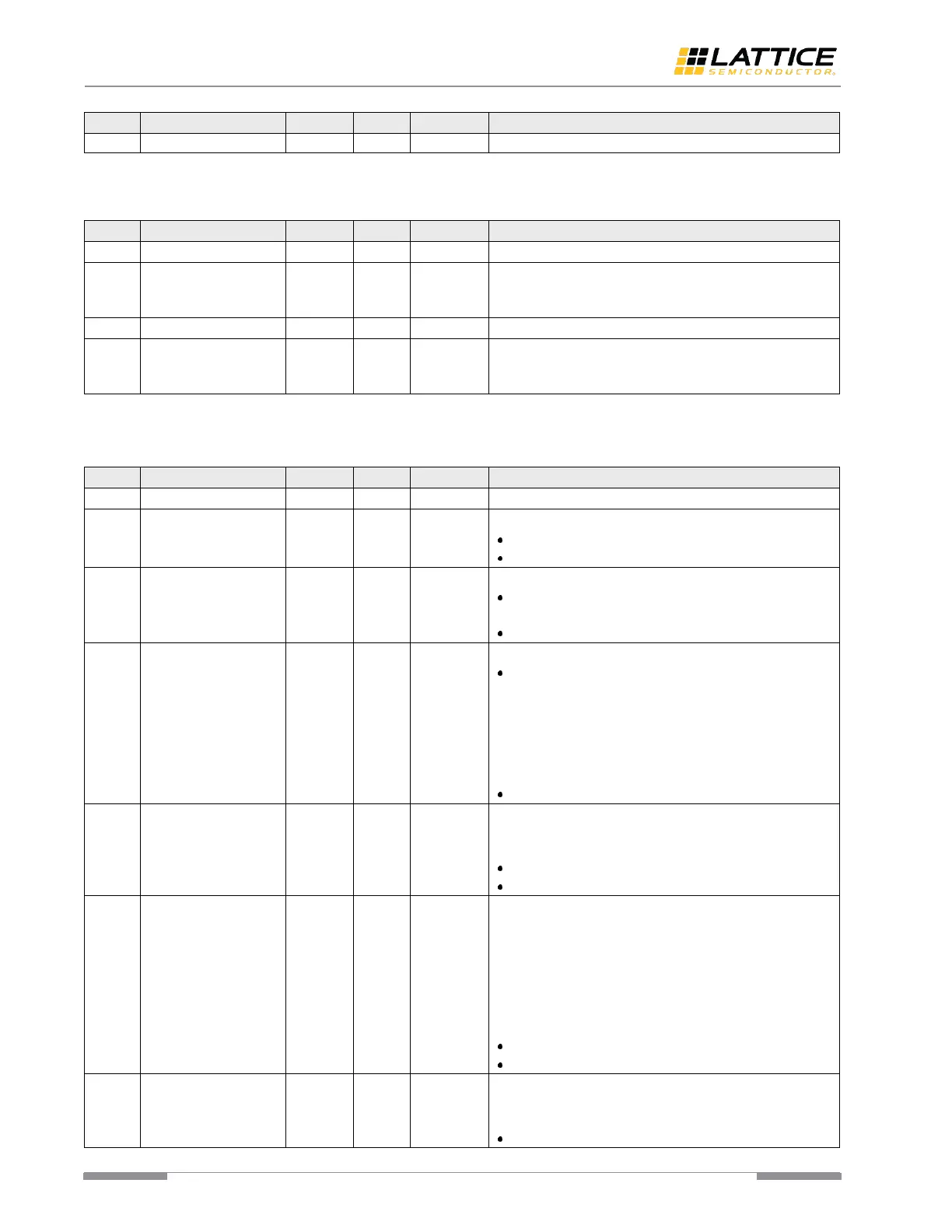

Table A. 25. Receive PLL Current Charge Pump [reg6a]

These bits define the Rx CDR PLL charge pump current

when the CDR PLL is frequency locked and running in PCIe

Gen1 speed or in any other non-PCIe protocols.

These bits define the Rx CDR PLL charge pump current

when the CDR PLL is phase locked and running in PCIe

Gen1 speed or in any other non-PCIe protocols.

Note: This register can be reprogrammed when the PHY is under reset.

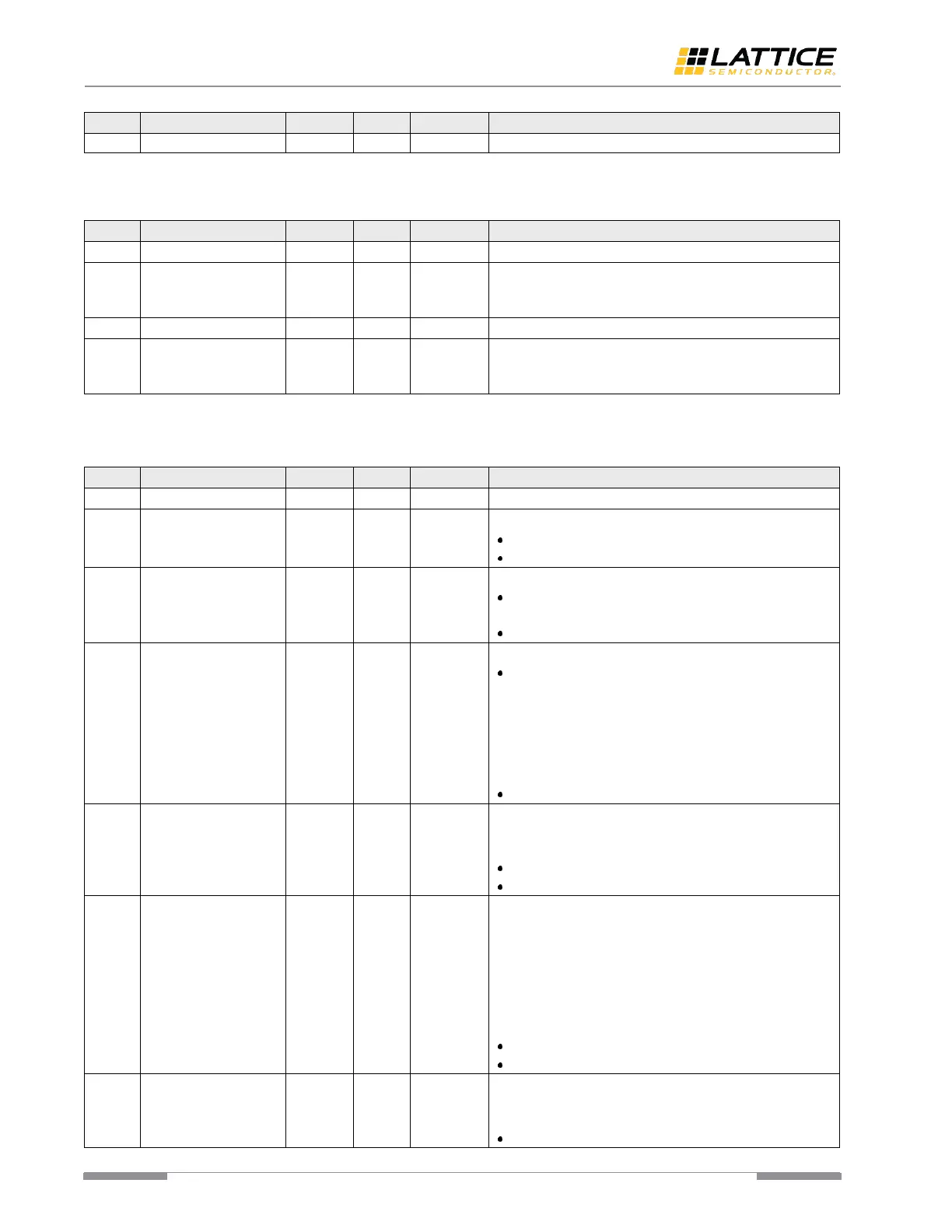

Table A. 26. PCS Loopback Control [reg74]

Rx data polarity control.

1’b1 – inverts the polarity of data on the received data.

1’b0 – normal operation.

Tx data polarity control.

1’b1 – inverts the polarity of data on the transmitted

data.

1’b0 – normal operation.

Far-end loopback control.

1’b1 – activates the far-end loopback through PCIe

elastic buffer fifo, assuming 0ppm between recovered

clock and transmitted clock. In case of different

reference clock, the PMA Tx PLL reference clock can use

the CDR clock, allowing to re-transmit loopback data

through the elastic buffer FIFO put in transparent

mode.

1’b0 – normal operation.

Reports if mesochronous clock alignment state machine

has completed its process, thus having aligned CDR

receive clock to transmit clock.

1’b1 – completed.

1’b0 – not yet completed.

Enables the mesochronous loopback mode which forces

PMA received data to be re-transmitted on the PMA Tx

interface. This mode requires that no PPM exists between

Rx data and Tx data (thus that both sides of the link use

the same reference clock), and performs alignment of CDR

clock to transmit clock using the PMA CDR PLL skip bit

functionality. This alignment is automatically performed

by a state machine when this loopback register is set.

1’b1 – enabling the mesochronous loopback mode,

1’b0 – normal operation.

Enables the parallel loopback mode which forces the

transmitted PIPE 10-bit encoded data to be loopback to

the receiver PIPE Rx interface.

1’b1 – enabling the parallel loopback mode.

Loading...

Loading...