CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

24 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

Table 5.5. 10GBASE-R Lane Mapping

Reference Clock Architecture

Each PMA Quad has four PMA channels. Each PMA channel has one independent Tx PLL and one independent CDR PLL.

However, all PMA channel share the same reference clock source. Each Quad requires its own reference clock, which

can be sourced externally from package pins, SDQx_REFCLKP/SDQx_REFCLKN, or from the FPGA internally.

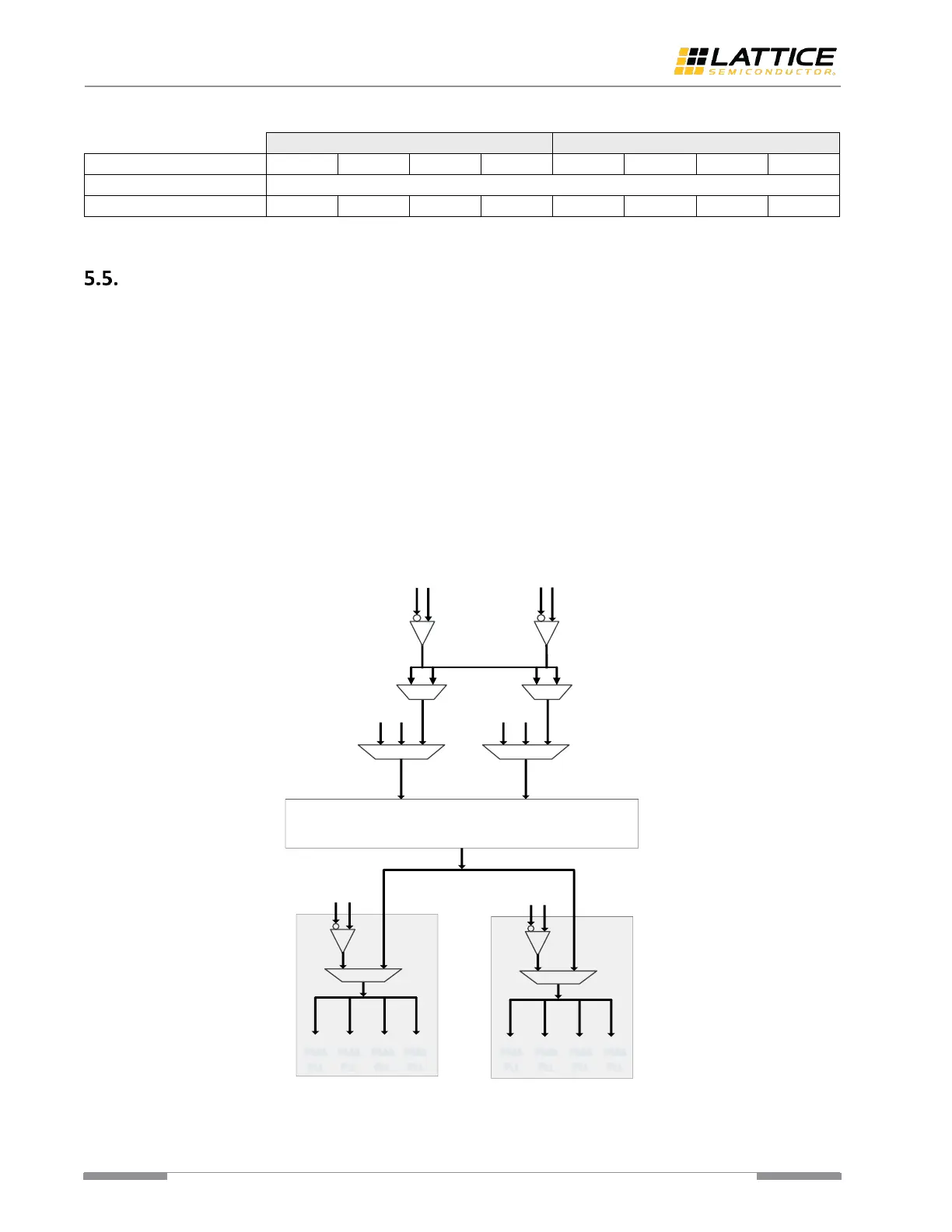

Figure 5.7 shows CertusPro-NX 100k device SerDes/PCS reference clock architecture. The Clock Tree block is designed

for balancing the skew between different Quads based on one reference clock source, and the skew between different

clock sources. The reference clock can source from General-purpose PLL (GPLL) output. You can use GPLL to form more

clock frequency division combinations. With the Clock Tree, different PMA Quads can use the same reference clock

source, which allows you to implement more than four lanes multi-lane serial protocols based on two or three PMA

Quads.

Each device also has two dedicated external reference clock input package pins, SD_EXTx_REFCLKP, SD_EXTx_REFCLKN,

which allow you to have more choices about the reference clock sources. Reference clock source from these two

dedicated pins or GPLL are needed when the number of lanes is larger than four (applications across the Quad).

Loading...

Loading...